硅材料CMOS器件由于硅本身的特性,并不适合用于高压大功率电子设备中,比如光伏逆变器、电动汽车充电桩和直流转换。然而,GaN因其拥有较高的禁带,能够提供更高功率以及更好的性能表现。因此,采用GaN材料的CMOS、HEMT器件能够更好的胜任这些应用。

硅衬底的结构及生长过程

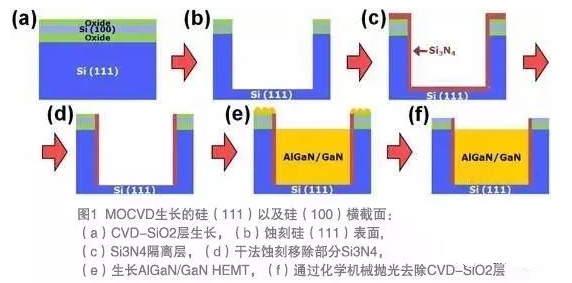

如图1所示,对于新的器件结构,研究人员首先采用750μm的硅(111)作为衬底,然后在其上生长145nm氧化层(SiO2)以及80nm的硅(100)层。通常,晶向为(111)的硅材料主要用于生长GaN,而硅(100)主要用于CMOS器件的应用。

其次,研究人员将硅(100)表面进行表面氧化,在表面形成40nm的氧化层(图1(a))。这样的结构更适合生长14nm工艺的CMOS。

然后研究人员在硅(111)表面蚀刻面积为200μmx200μm的区域作为GaN生长区域(图1(b))。

HEMT器件的生长过程

如图1(e),GaN与AlGaN材料同样采用了MOCVD工艺:(1)130nm 1050°C AlN层生长,(2)1.5μm 1035°C GaN缓冲层和沟道层生长,(3)1nm AlN 垫层、20nmAl0.25Ga0.75N阻挡层以及3nmGaN保护层生长。然后再在其表面生长3μm宽的栅极以及源极和漏极。

器件特性

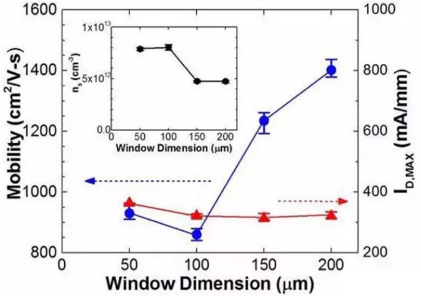

如图2,根据不同的蚀刻面积尺寸,电子迁移率也会随之变化。但是漏极电流的最大值却一直保持大致相同的水平(图中红色曲线)。研究人员表示,电子迁移率随着面积尺寸的减小而降低,是主要因为在较小面积的情况下,材料具有更强的应力松弛能力。

图2 GaN HEMT器电子迁移率和漏极电流特性图

同时,研究人员发现,电流崩塌效应在最大200μmx200μm的面积尺寸上的概率有所增加(小于25%),但是这个效应在较小面积的器件中只有不到6%。例如,通过实验测量,一个100μmx100μm面积尺寸的器件,其电流崩塌的概率只有不到2%。

研究人员认为,在这种图案化GaN器件中,电流崩塌似乎是与应力松弛有关,在较小的面积里,概率发生更低。尽管目前对于这种现象并没有准确的说明,但是研究人员相信缺陷和应力变化对于图案化GaN器件的电流崩塌存在重要的影响因素。