虽然很多研究团队都对这两种技术中的某一种进行了研究,但是有研究人员声称通过将这两项技术相结合,已经取得了较采用单一技术具有更好器件性能的研究结果。

作为详细介绍该项研究成果论文的第一作者,Yu- Lin Hsiao说道:“据我们所知,这是首次对在硅衬底上的AIGaN/GaN/AIGaN双异质结构中插入AlGaN中间层所进行的研究。”

由于插入了这一低温中间层,使得器件只受到较小的应力,从而具有更少的材料位错以及更高的击穿电压。引入双异质结构也提高了器件性能在GaN沟道中由于增加了对电子的束缚,将有助于降低在背阻挡层中的漏电流。

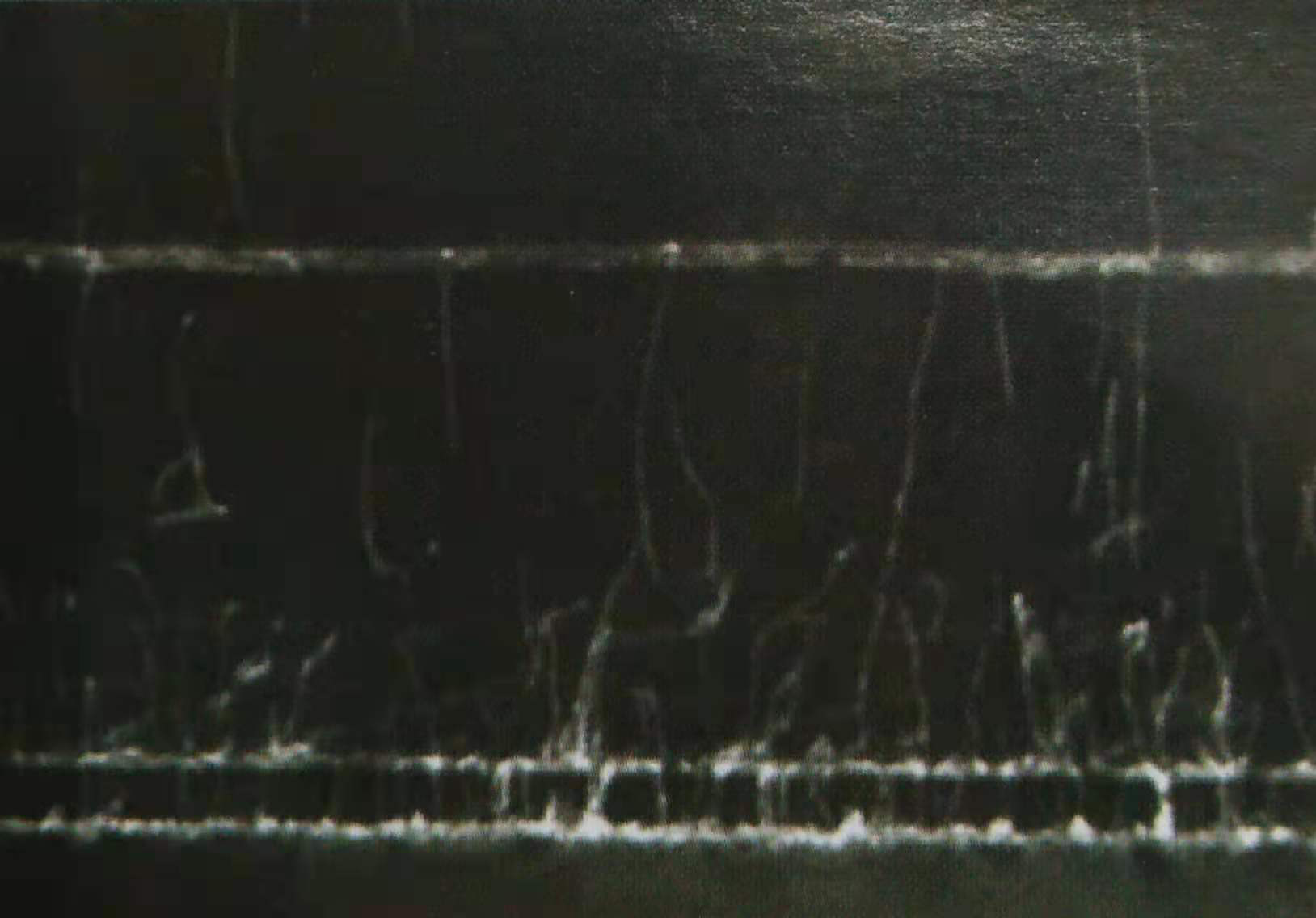

透射电子显微镜的截面照片表明,插入一个低温AGaN中间层能显著降低螺旋位错密度,这种螺旋位错密度的降低是非常有益的,因为这种类型的缺陷被认为是降低硅上GaN晶体管击穿电压的首要原因。

为了证明这种双管齐下方法的优越性,研究人员对三种不同结构器件的性能进行了评估:其中一种包含有一个双异质和一个低温中间层结构,而另外两种则要么是含有一个低温中间层和一个单异质结构,或是一个没有低温中间层的双异质结构。

所有这三种结构都是沉积在150mm硅衬底上,该衬底上有着800nm厚的过渡层,它是由一个AlN层和三个AIGaN层组成。 Hsiao解释说:“我们认为这是一种常见的过渡层结构,但是不同的团队所采用的过渡层的结构厚度可能有所不同”。台湾研究团队所插入的中间层是一个21nm厚的Al0.5Ga0.5N薄层,它是夹在两个1μm厚的Al0.1Ga0.9N层之间形成一种三明治结构。

Hsiao说道:“对于这种类型的结构而言,最为重要的是需要在不同生长温度和不同生长时间下对低温AIGaN中间层实现优化”,经优化后的中间层能够降低Al0.1Ga0.9N背阻挡层中的位错密度。

Hsiao解释说:“另一个重要的因素(尚有待确定)是插入这个低温AlGaN层的最佳时机,我们必须在第一层Al0.1Ga0.9N背阻挡层的生长过程中来获得其临界厚度”。为了确定这个厚度,我们采用了实时的曲率测量方法,它是由MOCVD系统中一个 Laytec EpiCurve TT仪器来进行测量的。

要最终完成双异质结构晶体管的生长过程,还需淀积一个90nm厚的沟道层和一个30nm厚的AL0.2Ga0.8N顶部阻挡层。对于具有单异质结构的对比试验样品来说,其器件是由一对GaN和AL0.2Ga0.8N层组成。

为了比较这三种器件结构的击穿电压,先采用干法刻蚀形成隔离区,然后利用电子束蒸发系统来沉积多层金属,然后在800℃的氮气中进行60s的快速热退火(RTA)。所形成器件栅极宽度为100μm,栅极长度为1μm,栅漏极间距为4.5μm,栅、源极间距为1.5μm。

与两种普通结构器件的击穿电压均低于400V相比,结合有低温中间层和双异质结构器件的击穿电压超过了600V。

该研究团队目前正计划在较厚的Al0.1Ga0.9N背阻挡层中插入两个或者更多的低温中间层,以进一步提高器件的击穿电压。