GaN基数字电路主要采用直接耦合场效应管逻辑(DCFL)来实现。2006年,Yong Cai等人应用F+离子处理技术实现了GaN E/D HEMT器件的集成,并且以DCFL逻辑设计了反相器和17级的振荡环电路(振荡环的工作电压为1V时,最小传输延时为130ps/stage,振荡频率为225MHz)。2013年,南京电子器件研究所应用栅挖槽工艺实现了GaN E/D HEMT器件的工艺集成,也应用DCFL逻辑设计了反相器和17级的振荡环(振荡环的工作电压为1V时,传播延时为146ps/stage,振荡频率为201MHz)。目前,D-mode GaN HEMT器件的工艺条件相对成熟,而高性能E-mode GaN HEMT器件的研制将是GaN E/D集成电路实现的关键。E-mode GaN HEMT器件不仅仅是实现DCFL逻辑的需要,同时它的性能对数字电路的特性有着决定性的作用。实现GaN E-mode HEMT器件的工艺主要有以下几种:F+离子处理技术,其优点在于工艺简单,容易集成,缺点是阈值电压的不确定性,存在一定的损伤,具有潜在的可靠性问题;栅挖槽技术,优点同样在于工艺简单,满足集成工艺要求,但是存在刻蚀深度控制要求高、阈值电压均匀性难控制的问题;p-GaN帽层技术,其优势在于阈值均匀性控制容易,由于其生长难度高且帽层较厚,不适合制造高频电路,一般应用于电力电子产品的制造中。

本实验采用选择性栅挖槽结合栅介质的工艺实现GaN E/D HEMT的单片集成,采用DCFL逻辑设计了反相器、与非门和或非门等数字逻辑门电路,采用栅挖槽工艺获得了相对高性能的GaN E-mode HEMT器件。但是,器件还存在着一些比较明显的问题,如阈值电压的漂移、阈值电压均匀性偏低、界面态影响明显等。文中将介绍基于选择性栅挖槽结合介质工艺制备得到的GaN E/D HEMT器件和数字逻辑门电路的特性,同时分析它们所存在的问题,为以后的研究提供借鉴。

1. 制备工艺及电路结构

GaN E/D集成工艺基于标准的AlGaN/GaN异质结材料结构,即25nm的Al0.25Ga0.75N势垒层、1nm的ALN插入层和3nm的GaN帽层,利用金属有机化学气相沉积(MOCVD)技术在蓝宝石衬底上外延生长获得,所有各层都非故意掺杂。对材料的载流子浓度和迁移率进行了霍尔效应测试,室温下异质结材料的2DEG面密度为9×1012cm-2、迁移率为1650cm2/(V·s),方阻为420Ω/□。

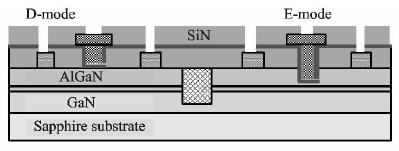

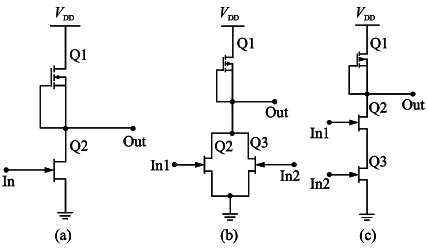

GaN E/D HEMT器件的集成采用选择性栅挖槽工艺来实现,器件结构示意图如图1所示。GaN E/DHEMT器件的源,漏和栅分别采用Ti/Al/Ni/Au和Ti/Au。为获得良好的欧姆接触,欧姆金属在880℃、N2气氛下进行了快速热退火处理。器件的隔离采用B+离子注入实现。采用等离子体增强化学汽相沉积(PECVD)生长的SiN对器件表面进行钝化。E-mode和D-mode器件的形成通过选择性栅挖槽的方法来实现。为了降低栅的漏电,采用原子层淀积(ALD)工艺在栅金属和势垒层间沉积一层10nm厚的Al2O3。在同一圆片上制备了GaN E/D集成HEMT器件和逻辑门电路,在每个设计单元中包括了不同尺寸(栅宽5~60μm,栅长为0.8μm)的GaN E/D HEMT器件、不同尺寸的反相器、与非门和或非门电路,其中DCFL反相器、与非门和或非门的电路结构示意图如图2所示。图2(a)为DCFL GaN E/D HEMT反相器的电路示意图,D-mode HEMT栅极与源极相连起一个负载管的作用,E-mode HEMT起一个驱动管的作用。

图1 选择性势垒减薄工艺实现GaN E/D器件集成的示意图

图2 DCFL电路示意图:(a)反相器;(b)或非门;(c)与非门

DCFL与非门与或非门的电路结构如图2的(b)、(c)所示,D-mode HEMT作为负载管,两个E-mode HEMT作为与非门与或非门的输入,输出的电压为E-mode HEMT上的分压。在电路的设计中,E-mode HEMT与D-mode HEMT器件尺寸的比例β[β=(Wg/Lg)E-mode/(Wg/Lg)D-mode]是最重要的物理参数。本实验设计了不同β值的电路,以研究其对电路特性的影响。

2. 测试结果及分析

2.1 GaN E/D HEMT器件特性

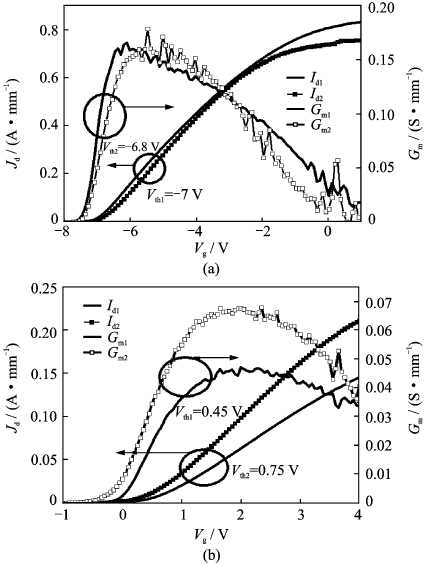

制得的GaN E/D HEMT器件的转移特性采用安捷伦B1500A进行测试,结果如图3所示。D-mode GaN HEMT的最大电流密度IDmax和峰值跨导gmax分别为0.76A/mm和175ms/mm,夹断电压为Vth=-7V。E-mode GaN HEMT的最大电流密度IDmax和峰值跨导gmax分别为0.25A/mm和70ms/mm,夹断电压为Vth=0.45V。E-mode器件的电流密度比较小,这是由于栅挖槽会对势垒层的表面造成损害,引入大量的界面态,同时SiN钝化层与器件表面之间也存在大量的界面态,界面态会耗尽一部分2DEG,直接导致了电流密度的减小。本实验为了得到大的栅压摆幅,采用的是MIS结构,沉积的Al2O3虽然会降低器件的跨导,但是有这层介质层,栅金属与沟道的距离更远了,栅金属对沟道载流子的控制能力变弱,使得D-mode器件的阈值电压会更负,而E-mode器件的阈值电压会趋向更正,即阈值电压的绝对值会变大,增大了器件的栅压摆幅,其中E-mode器件可以在7V的栅压下正常工作。

大的E-mode器件的阈值电压可以提高DCFL逻辑电路的“0”态输入噪声容限,但是在测试过程中发现器件在高栅压条件下工作一段时间之后,器件的阈值电压会有一定程度的正向偏移。如图3中(a)和(b)图所示,D-mode HEMTs的阈值电压由Vth1=-7V升到了Vth2=-6.8V,E-mode HEMTs的阈值电压由Vth1=0.45V升到了Vth2=0.75V。分析造成阈值电压漂移的一个主要原因是器件存在界面态。界面态主要来自于介质刻蚀过程中,器件的表面遭到损害而留下的悬挂键;其次SiN钝化层与势垒层之间也有很大的界面态,在器件通电时,界面态会充电,悬挂键会吸引器件沟道中的2DEG,从而进一步耗尽沟道中的2DEG,所以造成了器件阈值电压向正向偏移及器件电流密度的减小。界面态会极大的影响器件的特性,在实际的生产中要尽量减少器件的界面态。界面态可以通过改善刻蚀条件,优化介质生长和自氧化等方法得到改善。

图3 器件转移特性曲线图:(a)D-mode器件的转移特性;(b)E-mode器件的转移特性(Id2、Gm2为在经过高压以后,再次测量得到器件的转移特性)

测试中还发现器件存在着阈值电压不均匀的问题,这是栅挖槽的过程中,介质刻蚀的深度是非常难以控制的,如果介质刻蚀得过深,会导致器件的导通电流非常低,而介质刻蚀深度太浅,器件很可能没有实现增强型。这个问题可以通过优化刻蚀工艺,提高刻蚀设备的刻蚀精度来解决。

2.2 DCFL反相器

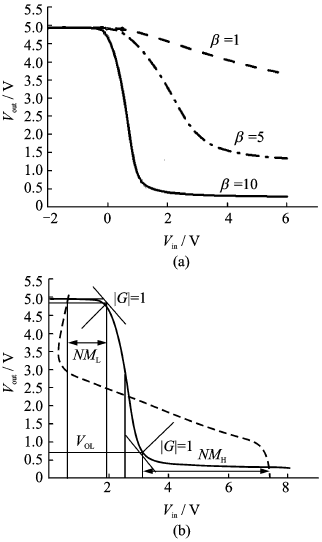

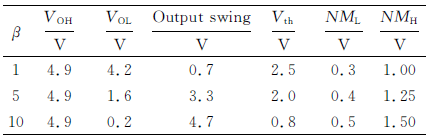

对不同β值的反相器电路进行测试,得到图4(a)和表1的结果。反相器的一些基本参数定义如图4(b)所示。VOH和VOL分别为反相器的逻辑高低电平值,Vth为反相器的阈值电压(高低电平转换的中点),nmL、nmH为反相器的噪声容限。

从测试的结果可以看出,逻辑门的偏压VDD的值决定了VOH的值,VOL的值随着β的增大而减小,输出电压的摆幅随着β变大而增大,反相器阈值电压随着β的增大而减小,同时噪声容限随着β的增大而增大。这是因为在DCFL逻辑中,E-mode HEMT输出电压就是门电路输出,β值越大,器件的栅宽越大,其导通电阻越小,所以在E-mode HEMT上分压值越小即输出电压越小。所以β值越大,反相器的直流输出特性越好,同时GaN器件较高的工作电压使得电路有更大的输出驱动能力。但是,随着β值的增大,电路输出延时会增加,需要设计者作出权衡。

表1 反相器电压输出特性

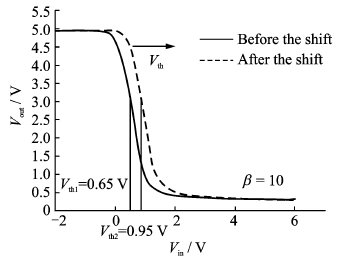

前文中提到器件的阈值电压在高压工作一段时间后,会有一个正向的漂移。阈值电压的漂移也会对反相器的特性有影响,其结果如图5,可以看到随着器件阈值电压的正向漂移,反相器的阈值电压也会正向漂移(Vth由原来的0.65V漂移到了0.95V)。这是因为反相器的阈值电压主要是取决于E-mode HEMT的阈值电压,由于器件阈值电压的漂移,从而导致了反相器阈值电压的漂移。

图5 反相器的阈值电压漂移

2.3 DCFL与非门和或非门

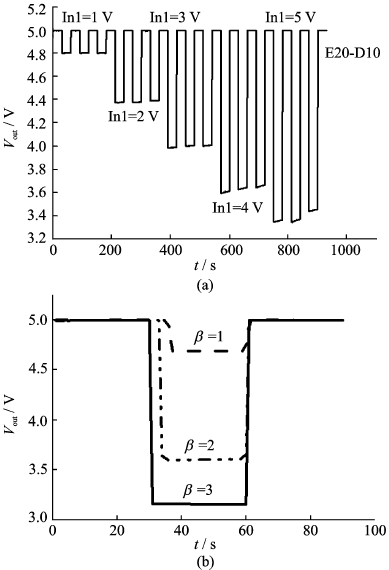

圆片上制备了不同器件比例(β)的或非门和与非门,并对它们的特性进行测试。在测试或非门时,In2置于0V(逻辑低电平),改变In1的输入值来观察电路的逻辑功能的实现情况。在测试与非门时,In2置于5V(逻辑高电平),改变In1的输入值来观察逻辑功能的实现情况。或非门的逻辑实现情况如图6(a)所示,该电路的器件比例为D10-E20(β=2,耗尽型器件栅宽10μm,增强型器件栅宽20μm),电压的摆幅随着In1的增大而增大,这是由于随着输入电压的增大,E-mode HEMT的载流子浓度变大,导通的电阻变小,导致E-mode HEMT的分压变小,输出电压变小。在改变β值时,测试结果如图6(b)所示,随着β值的变大,电压的摆幅变大。因为E-mode HEMT的器件尺寸变大,器件的导通电阻变小,分压变小,输出电压变小。与非门的输出特性与或非门的类似,在改变β值时,也会有与或非门相似的特性,但是电压的摆幅会不同。由实验可知β值越大逻辑门的转移特性越好,但β值的增大也伴随着电路延时的增加,电路设计者要在两者之间做出权衡。

图6 或非门的输出特性:(a)V-t特性;(b)不同β值的V-t特性

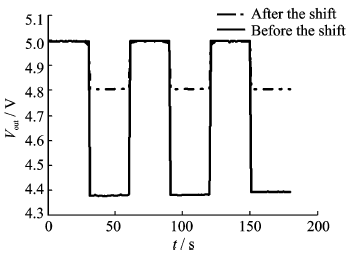

器件阈值电压漂移会对电路特性有影响,其特性如图7所示。当In2=0V时,Vout1为阈值电压漂移前的输出特性,Vout2为阈值电压漂移后的输出特性。在阈值电压正向漂移后,电路在In1=1V时,电压摆幅有明显的减少。这是由于在阈值电压漂移后,In1=1V时E-mode HEMT还没有完全导通,器件的导通电阻相对于漂移前大,导致E-mode器件的分压变大,输出电压变大。输出电压的摆幅减小会导致电路的噪声容限变小,更严重的当电路工作在较低的电平时,电路的逻辑功能可能无法实现。所以,实现阈值电压的稳定是研制高质量GaN E/D HEMT集成数字电路的前提条件。

图7 阈值电压漂移对逻辑电路特性的影响

3. 结论

采用选择性栅挖槽工艺实现了GaN E/D HEMT器件的集成,并且用DCFL逻辑设计了GaN E/D HEMT反相器、与非门和或非门。制备得到D-mode GaN HEMT器件的最大电流密度IDmax和峰值跨导gmax分别为0.76A/mm和175ms/mm,夹断电压为Vth=-7V。E-mode GaN HEMT器件的最大电流密度IDmax和峰值跨导gmax分别为0.25A/mm和70ms/mm,夹断电压为Vth=0.45V。同时发现器件在高栅压下工作一段时间后,阈值电压会正向漂移,这主要是由于器件的界面态造成的。制备的逻辑门电路可以较好地实现逻辑功能,发现电路的β值越大,逻辑门的转移特性越好,但是,β值的增大会增加电路的输出延时,降低电路的速度,要求电路设计者在两者之间做出权衡。同时,器件的阈值电压漂移会造成逻辑功能在低电压下工作状态下不稳定。由实验可知界面态对器件和电路的特性会有很大的影响,所以找到一个精确表征界面态的方法会对器件工艺的改进有很大的帮助,这也正是下一步工作的重点之一。