在某民用功率放大产品的试制中,由于指标需要实现高于普通功率放大的功率,因此使用氮化镓器件进行研究与试制。

本次使用的氮化镓芯片,在28V下功率60W,在硅衬底上生长,背面电镀3μm厚的金。鉴于功率器件需要良好的散热,本次试制的目标是将其组装在钨铜载体上,从芯片热膨胀系数的匹配性以及组装面的处理情况这两方面考虑,其组装可使用共晶或者功率导电胶粘接的方法。

共晶焊接是微电子组装中一种重要的工艺,也称低熔点合金焊,具有机械强度高、热阻小、传热快、饱和压降小、稳定性好及可靠性高等优点。它能避免采用环氧树脂和银浆进行粘片产生的在高温下变脆和易挥发而污染芯片的缺点。也克服了用导电胶粘片抗温度及机械冲击性能差和长时间存放芯片易脱落的弊病。

由于共晶焊接在上述方面优于导电胶粘片,本文选取了共晶焊接的方式进行组装氮化镓芯片的试验,并对其进行了研究,给出了目前技术水平条件下的共晶焊接情况。

1. 工艺方案

1.1 共晶方法

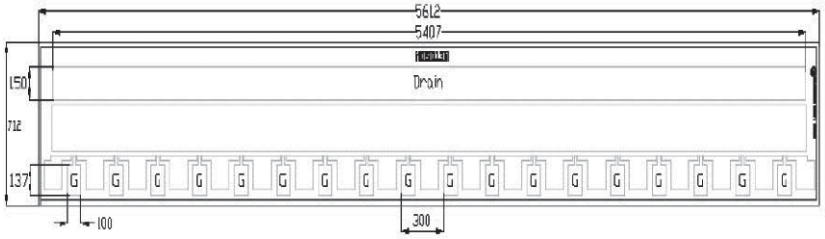

本次试验氮化镓芯片如图1所示。

图1 试验芯片(单位:μm)

目前共晶焊接普遍使用的方法是采用合金焊料将元器件与基板进行共熔,通常情况下,采用金锡、金锗、金硅作为合金焊料。但由于本次试验被焊芯片材料的特殊性,其焊接面已经含有了Au和Si,可采用无焊料共晶的方法进行焊接,即在基板上不使用合金焊料,利用氮化镓芯片衬底的Si和镀金层在高温下形成Au-Si共熔晶体,从而直接达到芯片焊接的目的。从芯片散热以及热应力角度考虑,选用热传导率较高且热膨胀系数匹配的钨铜载体作为基板。

1.2 本试验的难点

考虑氮化镓材料本身及试验芯片的特点,本次试验的难点在于:1)氮化镓材料薄且脆,试验芯片价值昂贵,共晶操作难度及压力较大;2)由于功率为60W,芯片的源极有很多接地通孔,必须很好地控制共晶的温度和时间,在保证芯片良好接地的同时,又要防止熔化的金硅合金从通孔溢到芯片表面,造成沟道短路。

1.3 工艺要素

共晶焊接的要素包括焊接温度、焊接时间、压力、擦动频率及幅度、保护气氛等,必须从这些方面进行优化试验。

焊接时,由于热量传递条件、温度测量误差等影响,焊接温度应高于Au-Si共熔点,在适当提高焊接温度的同时,应对钨铜载体进行足够的预热。工艺采用的保护气体也应适当加热,以免降低焊区的温度。焊接温度过高,会使芯片特性变坏,操作条件恶化,导致共熔体表面氧化。因此,结合Au、Si二元系相图,选定操作温度不宜超过420℃。同时,在焊接时要定时用表面温度计来测量表面温度,保证焊接质量和工艺重复性。

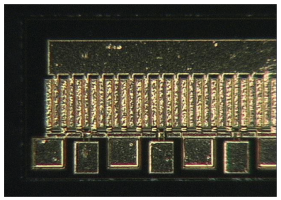

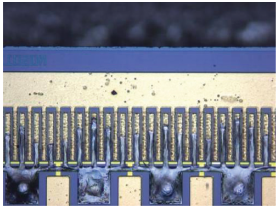

此外,焊接时间不宜过长,否则会造成共熔晶体的氧化以及影响芯片的特性。氮化镓芯片薄且脆,并且试验芯片(如图2所示)的源极有很多接地通孔,在高温下超过一定的时间,熔化的Au-Si合金会通过通孔溢出到芯片表面,造成沟道的短路,如图3所示。因此,要特别控制好共晶焊接的时间,避免损坏芯片。

图2 试验芯片

图3 Au-Si溢到沟道造成短路

焊接时应使芯片在一定的压力和幅度下摩擦,这样可以减少芯片与底座之间由于表面不平所造成的空隙的影响。同时,压力和擦动可以使液态的合金均匀地浸润在芯片与底座的结合界面上,减少虚焊和焊接空洞,保证焊接面积。在手动焊接时,要轻拿轻放,以免损伤芯片。

进行共晶焊接时,空气中的氧气或其他有害气体将导致芯片表面和基板表面氧化或发生其他化学反应。焊接时采用了氮气和氢气的混合气体。其中氮气是惰性气体,能防止氧化,而氢气能对已氧化的表面起还原作用。为了使保护气体在共晶的范围内流动,减少气体的损失,在操作的加热台表面制作夹具设计了一个保护区域。

综合以上三个方面,本次试验应从共晶的几个参数上进行不同的组合。在共晶过程中针对氮化镓材料薄、脆的特点需掌握相应的操作力度。由于本试验芯片的特殊性,要特别控制好共晶时间。

2. 工艺试验

2.1 参数选取

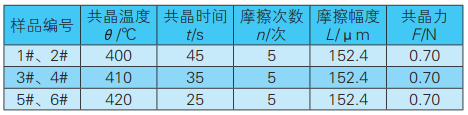

从焊接温度、焊接时间、压力、擦动频率和幅度几个要素选取3组不同的参数组合进行试验,见表1。

表1 试验参数

2.2 试验结果

试验后,进行超声扫描,检测共晶面的空洞及分层情况。测试芯片剪切强度,按照军标要求,该试验芯片的剪切强度应大于24.5 N。对焊点质量进行切片检测。

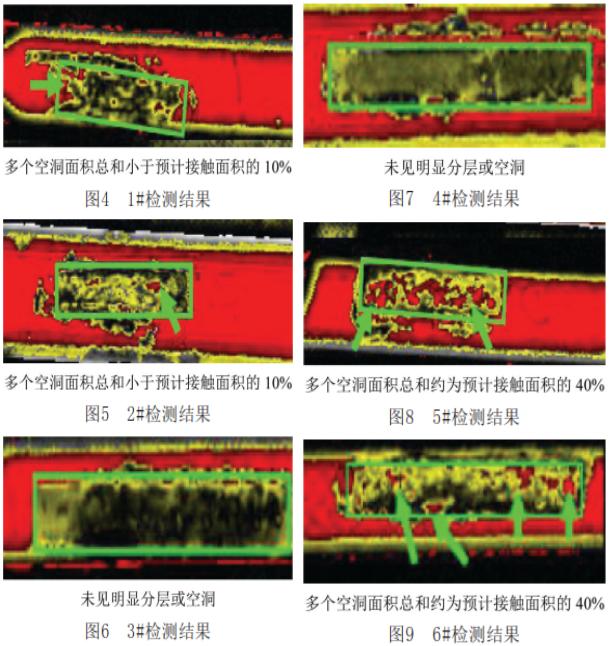

超声扫描检测的结果如图4~图9所示。

该试验芯片为功率器件,空洞率应满足低于预计接触面积10%的要求。根据超声扫描的结果可以看出,除5#、6#样品不满足要求外,其他4件样品均满足要求,其中3#与4#样品的共晶效果最好,均未见明显分层或空洞。

对所有试验件进行非破坏性剪切强度测试,均满足24.5N的要求,可见3组参数的共晶强度都达到了要求。

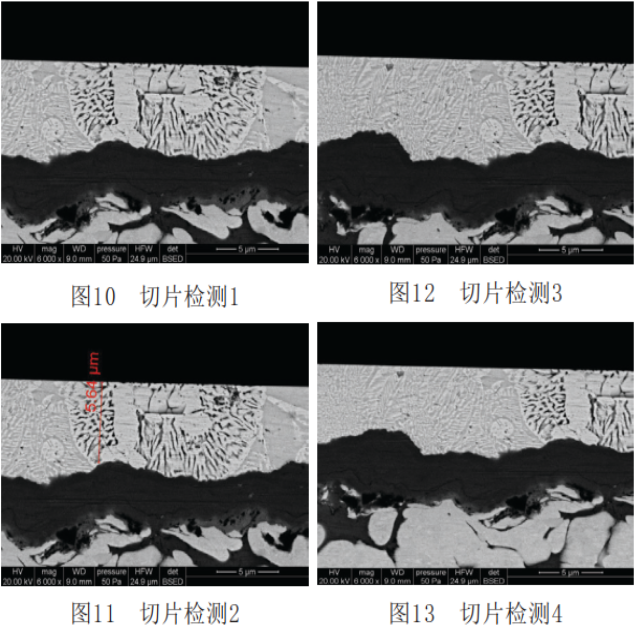

之后取超声扫描效果最好的两件样品中的4#样品对其不同的地方进行切片测试,焊点质量均好,结果如图10~图13所示。

由切片测试结果看出,焊点形成的枝状结构均匀致密,形成了良好的焊接。

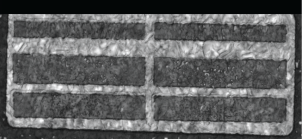

在剪切强度均合格的情况下,通过超声扫描和切片检测可以看出3#及4#的工艺参数是较为理想的。可以选取相同的参数进行重复试验,重复试验后超声扫描结果如图14所示。

图14 重复试验超声扫描结果

重复试验的超声扫描结果为未见明显的分层或空洞。剪切强度测试也满足要求,切片检测焊点质量良好,这表明选取的工艺参数能够较好地实现氮化镓器件的共晶焊接。

3. 结论

本文针对试验用氮化镓功率芯片的特点,分析了共晶焊接的工艺影响条件。选取不同的工艺参数,采用了保护气氛的方式进行试验,得到了以硅为衬底,底面镀金的氮化镓芯片直接共晶在钨铜载体上较为理想的参数,较好地实现了功率型氮化镓芯片的共晶焊接。证明氮化镓功率器件共晶焊接技术可行,为其将来的使用打下了基础。