本文对比常规单异质结HEMTs和AlGaN/GaN/AlGaN双异质结HEMTs器件的在电应力条件下的退化现象,并解释其机理。由于影响器件电应力退化的机制包括热载流子效应、栅电子注入以及逆压电效应等,为了单一分析热电子注入效应对器件退化的影响,我们采用HP4156B半导体参数分析仪对器件进行漏源电压应力测试,测试条件为源接地,栅悬空,漏极加电压VDS=20V,应力时间为30000s,在这种应力条件下,只有热载流子效应对器件退化的影响。在加应力之前先测试器件的直流特性,加上应力30000s后再进行测试,从而对比应力前后器件的退化程度。

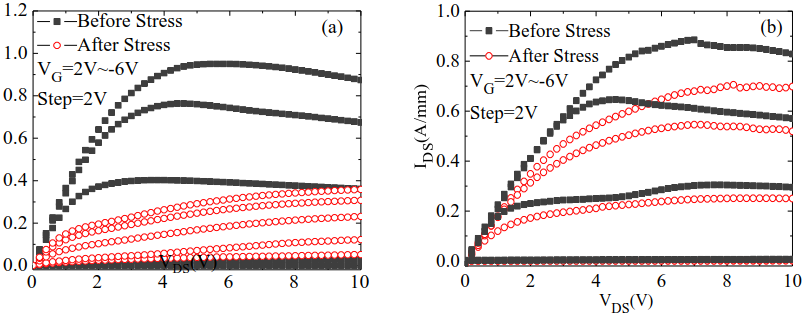

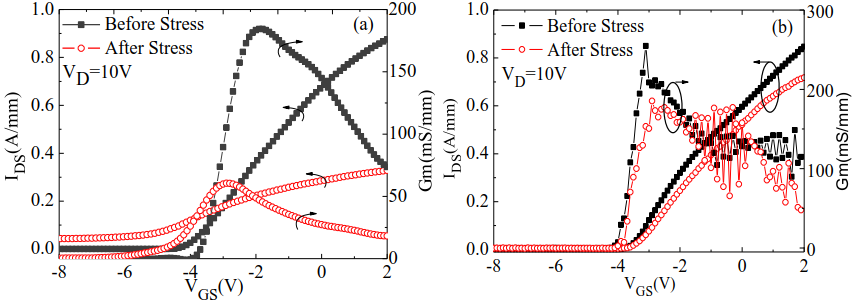

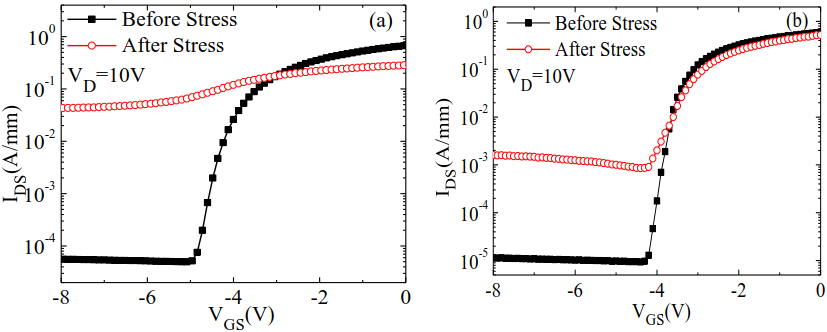

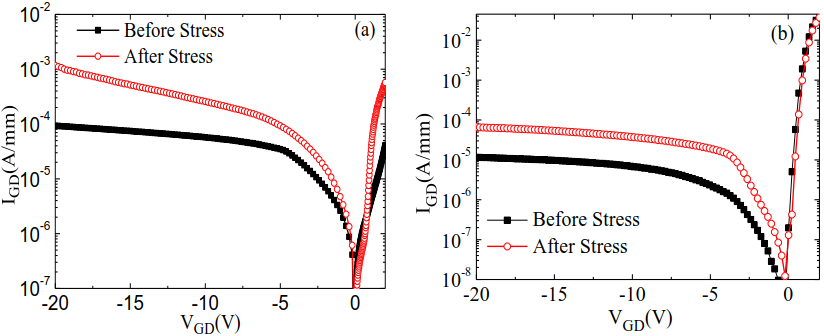

如图1、图2、图3、图4为常规单异质结HEMTs和双异质结HEMTs器件在直流电应力条件下的退化现象,主要包括饱和电流密度和跨导的降低、阈值电压的漂移、关态泄漏电流的增大以及肖特基反向漏电的增大。图1可以看出,在同样的应力条件下,常规单异质结HEMTs器件在应力前后的饱和电流密度IDmax分别为874mA/mm和358mA/mm,降低了大约60%,而双异质结HEMTs器件IDmax从829mA/mm和698mA/mm,只降低了大约16%。图2中,常规单异质结HEMTs和双异质结HEMTs器件的峰值跨导分别降低了67%和27%,应力后常规单异质结HEMTs器件已经无法关断,而双异质结HEMTs器件的阈值电压变化比较小。图3中,在VD=10V、VGS=-8V时常规单异质结HEMTs器件的关态漏电从5.6×10-5A/mm增加到4.3×10-2A/mm,增加了近3个数量级,而双异质结HEMTs器件的关态漏电增加了2个数量级。图4中,常规单异质结HEMTs的肖特基反向漏电在应力前后分别为9.3×10-5A/mm和1.2×10-3A/mm,双异质结HEMTs肖特基反向漏电分别为1.2×10-5A/mm和6.5×10-5A/mm,应力前后两种结构的肖特基反向漏电均增大。

图1 应力前后两种异质结构输出特性曲线的变化,(a)SH-HEMTs,(b)DH-HEMTs

图2 应力前后两种异质结构转移特性曲线的变化,(a)SH-HEMTs,(b)DH-HEMTs

图3 应力前后两种异质结构关态漏电的变化,(a)SH-HEMTs,(b)DH-HEMTs

图4 应力前后两种异质结构肖特基反向漏电的变化,(a)SH-HEMTs,(b)DH-HEMTs

热电子注入效应是在Si器件和GaAs器件中一种非常重要的退化机制,后来发现热电子注入效应能够很好地解释GaN基HEMTs器件中的一些退化现象,因此也受到越来越多的重视。所谓热载电子注入,就是当电子从外界获得了很大能量时,如在强电场作用下,电子沿着电场方向不断运动和加速从而成为热电子,这些热电子与晶格发生弹性碰撞以后改变运动方向,被表面陷阱或缓冲层陷阱所俘获,使器件性能降低。沟道中的热电子一部分进入AlGaN势垒层,一部分进入沟道下方的缓冲层中。对于常规单异质结HEMTs器件,GaN缓冲层一侧的势垒高度较低,载流子限域性较差,因此大部分沟道热电子会注入到缓冲层中成为低迁移率的三维电子,并被缓冲层中的深能级陷阱甚至浅能级陷阱所俘获,最终使得器件的关态漏电显著增大,沟道无法夹断。沟道热电子注入到缓冲层后成为三维电子,使得整个电子系统中的2DEG密度和迁移率显著降低,从而使器件饱和电流密度和跨导严重退化。而对于双异质结HEMTs器件,由于采用AlGaN缓冲层,沟道下方的背势垒高度显著提高,载流子限域性增强,抑制了热电子进入到缓冲层中,因此关态漏电和阈值电压的退化并没有像常规单异质结器件的退化那么大,而且饱和电流密度和跨导的降低也比较小。

同时,还有另外一部分沟道热电子与晶格碰撞后注入到AlGaN势垒层中,但是由于势垒层中极化电场的作用,应力结束后大部分热电子会返回到沟道中,只有少数电子被AlGaN势垒层中的深能级陷阱所俘获并不能返回到沟道中,这些被俘获的电子通过陷阱辅助隧穿作用[4.25]使得器件的肖特基反向漏电增加。因此两种异质结构的肖特基反向漏电均增大了,但是变化范围都在一个数量级以内。我们认为,由于双异质结势垒层的相对应变减弱,在相同的电压下势垒层中的缺陷较小,因此双异质结肖特基反向漏电较小。

可见,采用AlGaN/GaN/AlGaN双异质结构,由于背势垒高度的提高和载流子限域性的增强,器件退化程度明显减弱,尤其是关态漏电和阈值电压。采用双异质结构是抑制热电子注入的一种有效的方法,另外提高缓冲层和势垒层的结晶质量也可以在一定程度上减弱热电子注入对器件退化的影响。