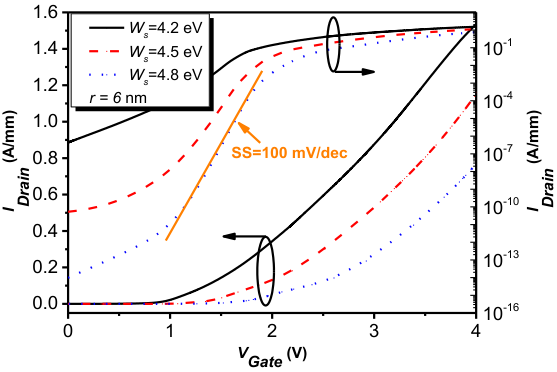

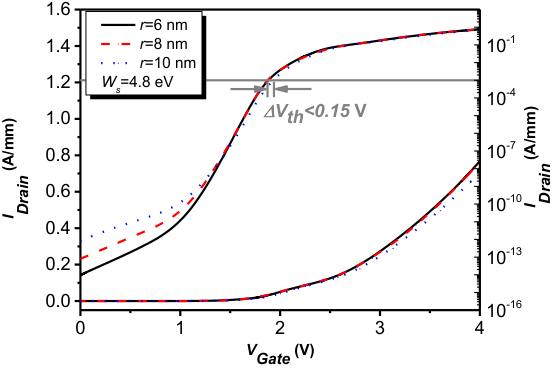

SFG-FET在相同凹槽深度下的转移特性如图1所示,从图中可以看出漏电与饱和电流随源极肖特基金属功函数变化的趋势,即源极金属功函数越高SFG-FET的漏电越小且电流输运能力越低。值得注意的是,当源极功函数为4.8eV时,器件具有较低的亚阈区摆幅(约为100mV/dec)

图1 相同栅凹槽深度下SFG-FET的转移特性

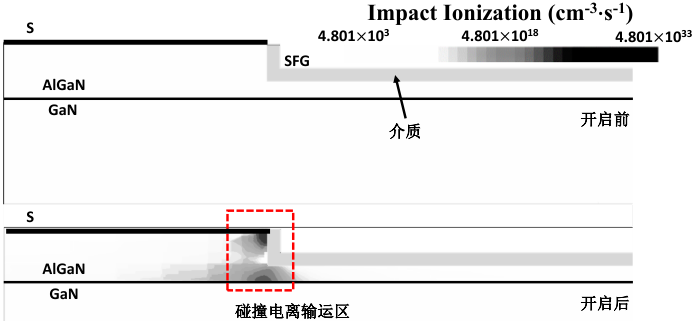

图2 栅极开启前后源极附近SFG-FET的碰撞电离率分布

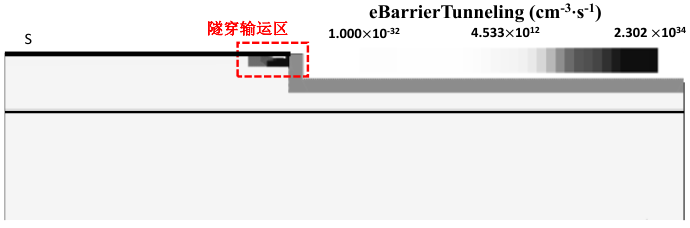

图3 栅开启后源极附近SFG-FET的隧穿概率分布

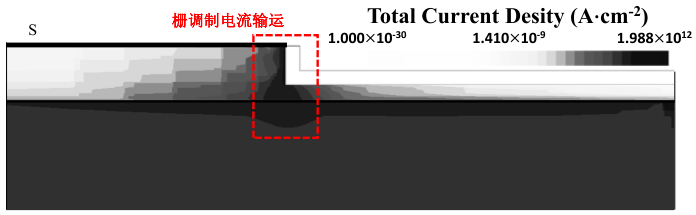

这个结果是在对GaN层设置了较严苛的受主型陷阱密度基础上得到的,在真实情况下,由于碰撞电离的帮助,器件应该具有更低的亚阈区摆幅。图2所示的是器件开启前后(即栅电压在阈值前后)源极附近的碰撞电离率变化,当栅极电压正偏时,在源极下方发生了碰撞电离。碰撞电离主要发生在隧穿电子刚进入势垒层的区域以及SFG下方。图3所示的是栅开启后源极附近隧穿发生的概率,可以看出隧穿输运在SFG的调制下电子有大概率从源极金属隧穿入AlGaN层。结合图2与图3可以明显看出SFG-FET的栅调制隧穿-碰撞电离电流输运模式,其导通电流分布如图4所示。

图4 栅开启后源极附近SFG-FET的电流密度分布

图5 不同SFG深度下SFG-FET的转移特性

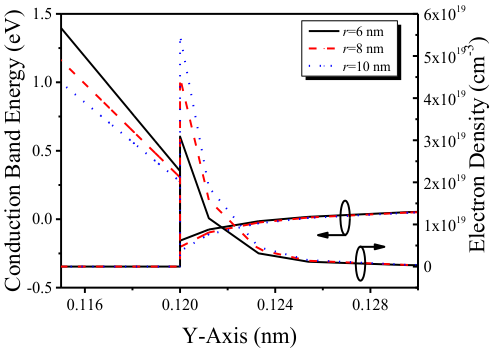

图5所示的是当SFG-FET源极金属功函数为4.8eV时不同SFG凹槽深度下的器件转移特性。从仿真结果中可以看到,当SFG下势垒层剩余厚度r在4nm范围内变化时,SFG-FET阈值变化小于0.15V。这说明了SFG-FET器件具有极强的刻蚀深度容错性,在SFG刻蚀深度在数个纳米内变化时,器件阈值电压与输运电流能力基本不受影响。这种容错性可以通过SFG下能带图与2DEG分布说明。

图6 不同SFG深度下SFG下的能带与2DEG浓度分布

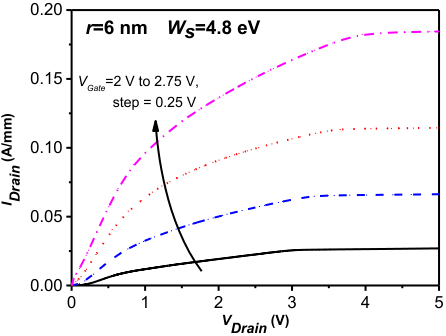

图7 SFG-FET的输出特性

图6是SFG下导带与2DEG浓度的分布示意图,从中可以看出当SFG凹槽下势垒层剩余厚度在6nm到10nm之间变化时,其下沟道处导带的变化并不大,这使得2DEG的浓度仅在一个数量级范围内变化,因此SFG对电流输运能力和阈值电压影响很小。这个特性在工业化生产中意义重大,即SFG-FET在快速干法刻蚀速率有误差的条件下依然能够保持较强的阈值电压稳定性。另外图6中线条接近折线而非曲线,这是为了加快仿真对Mesh进行了稀疏优化之故。

图7所示的是当SFG下势垒层剩余厚度r为6nm且源极金属功函数为4.8eV时SFG-FET的输出特性。当栅压为2.75V时器件的导通电阻约为9Ω·mm,可见SFG-FET的源极虽然是肖特基接触,但其导通损耗仍旧较低。