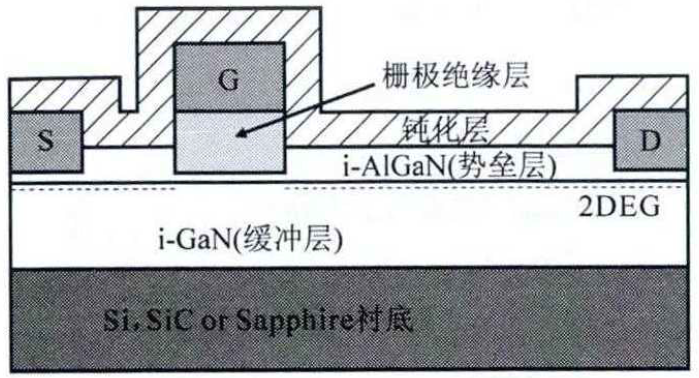

图1 AlGaN/GaN MIS/MOS-HEMT器件结构

1. 增强型器件技术

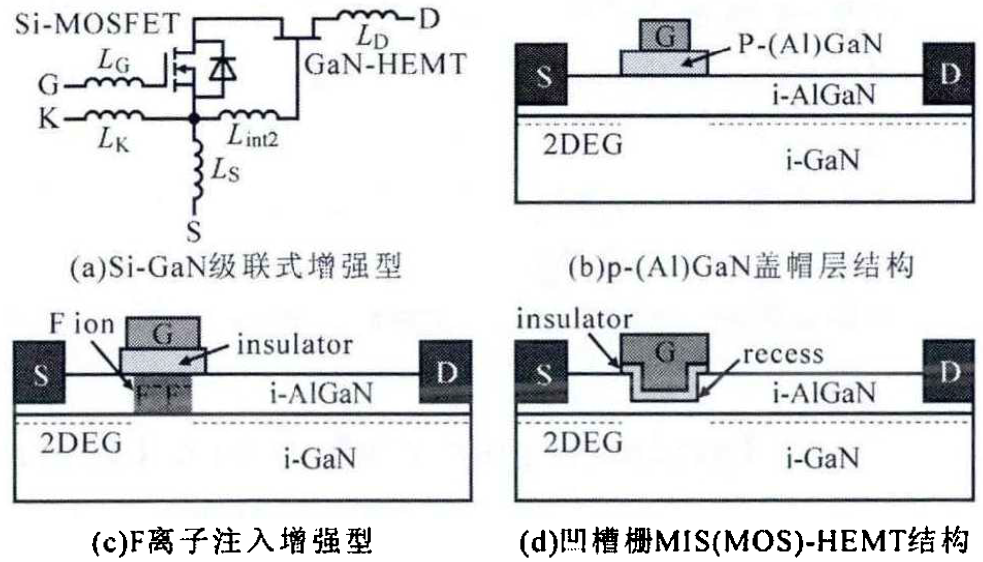

增强型(常关型)是功率开关系统失效安全的核心要求。目前GaN基平面功率开关器件的增强型结构主要有4种:

(1)增强型Si-MOSFET与GaN-HEMT级联结构该技术避开了GaN增强型难点,采用低压Si-MOSFET实现增强型,利用耗尽型GaN-HEMT实现高耐压,再通过键合技术级联成增强型功率开关器件,如图2a所示。但Si与GaN芯片间的键合封装不可避免会引入寄生电感等,制约了GaN基功率开关器件的高频应用(300kHz以上)。

(2)p-(Al)GaN盖帽层结构 该技术利用pn结形成的空间电荷区扩展耗尽栅下的2DEG,如图2b所示。该技术能将器件阈值推进到1.5V,但通常不会超过2V,主要局限是pn结的正向开启导致栅极正向漏电增大。

(3)F离子注入增强型MIS-HEMT结构 该技术通过在AlGaN势垒层中注入带负电的F离子,以耗尽沟道中的2DEG,如图2c所示。结合MIS-HEMT技术,该技术也能将阈值推进到3V以上。但F离子注入深度较难控制,在AlGaN/GaN异质结附近的拖尾可能会造成2DEG输运性能降低。

(4)基于凹槽栅技术的MIS-HEMT或Hybrid MOS-HEMT结构 该技术主要通过减薄AlGaN势垒层以削弱其极化强度,从而耗尽栅下的2DEG,如图2d所示。由于栅槽刻蚀不可避免导致较大的栅肖特基接触漏电,故通常采用MIS(MOS)-HEMT结构,该结构不仅能有效抑制栅极漏电,且能提高器件的阈值电压。刻蚀损伤、可控性和残留物的处理是该技术面临的主要挑战。

图2 GaN基平面功率开关器件结构

2. 表面与界面工程

新型宽禁带半导体GaN的性质:①GaN具有很强的自发和压电极化,表面存在高密度极化电荷;②在GaN表面很难制备出高质量的本征绝缘层。目前介质层/(Al)GaN界面态密度最低只能达到1012cm-2,不及SiO2(热氧化)/Si系统的1010~1011cm-2水平。悬挂键、表面氧化、氮空位、界面晶格无序是GaN基器件表界面态的几种可能来源。

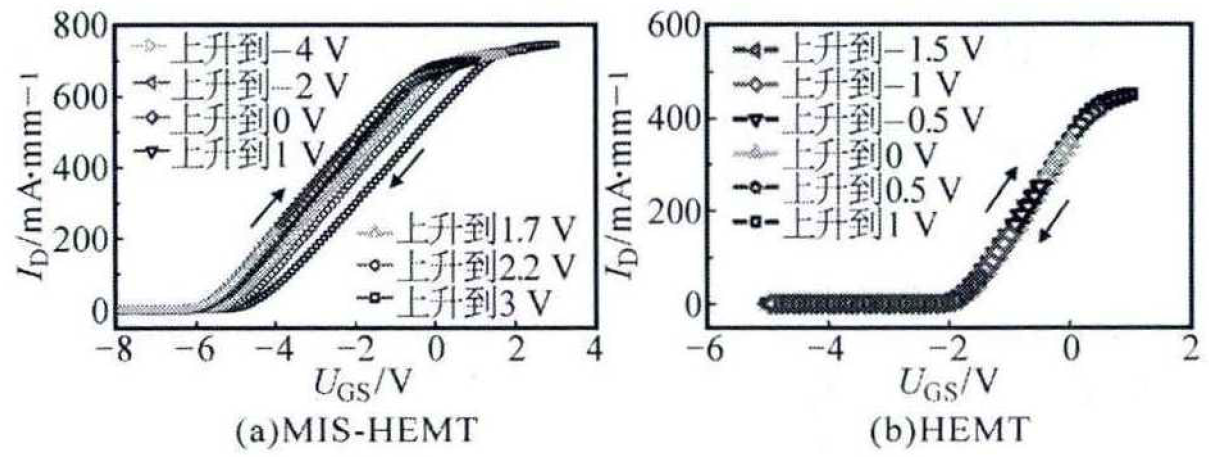

考虑GaN的高禁带宽度,其界面态能级位置也较深,故具有很长的发射时间常数。这种深界面态对绝缘栅GaN基电子器件的影响主要体现在两方面。一方面会导致栅极阈值漂移,在栅极开关转换过程中,深能级界面态的缓慢放电会导致MIS-HEMT器件阈值不稳定性,见图3a。类似现象在图3b中HEMT器件(肖特基栅)不能观察到。

图3 不同UGS,max时的转移特性曲线。

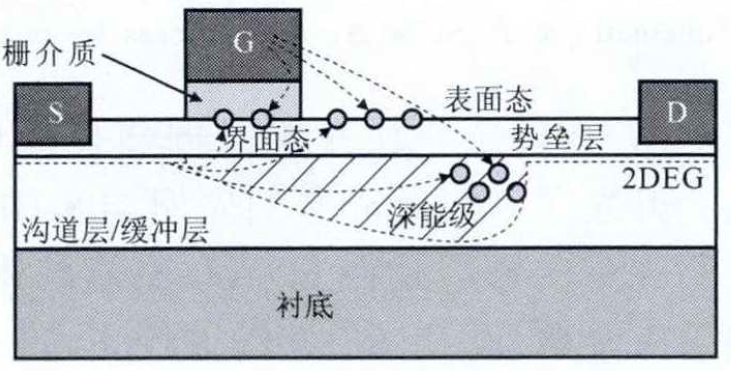

另一个影响是电流坍塌,GaN基平面型功率管在工作中通常会经历关态和高漏极偏置工作状态,在这些状态下构成栅极漏电的电子和从源极注入的电子在栅(源)漏间高场作用下,可能会注入到栅介质与势垒层间的界面态,栅漏间势垒层的表面态,甚至是2DEG沟道下缓冲层的深能级中,见图4。当器件回到开态、低漏极偏置工作状态时,由于表/界面态和缓冲层中深能级放电时间常数较长,跟不上器件的高频开关速度,2DEG—直处于被耗尽状态,从而导致器件的电流输出能力下降(电流崩塌)。对GaN基微波功率放大器,电流坍塌表现为DC-RF频散,输出功率严重压缩;对功率开关器件,电流坍塌表现为动态导通电阻急剧增加,动态损耗变大,电能转换效率下降。

图4 AlGaN/GaN MIS-HEMT电流崩塌效应图

为抑制由深界面态导致的阈值漂移,研发出原位低损伤GaN表面处理技术远程等离子体预处理(RPP)。先采用NH3/Ar远程等离子体去除(Al)GaN表面的自然氧化层,再进行N2等离子体处理补偿近表面的N空位,再淀积一层ALD-Al2O3栅介质。X射线光电子能谱表征证实NH3/Ar/N2原位处理能有效去除GaN表面的Ga-O键,尤其是充分的氮化处理能防止氧化物栅介质淀积造成的表面再氧化。低损伤RPP工艺在ALD-Al2O3和GaN界面产生一层近似单晶的AlN插入层(约0.7nm),使Al2O3/(Al)GaN界面态密度降至2×1012cm-2(0.35eV<Ec-ET<0.85eV),有效抑制了由氧化界面态导致的阈值漂移。

在RPP对(Al)GaN表面处理的基础上,采用PEALD技术,在AlGaN/GaN异质结构上低温(~300℃)生长出4nm近似单晶的AlN薄膜。准静态C-V测试证实采用该技术制备的髙晶体质量AlN能在其与(Al)GaN势垒层界面诱导出高达3.2×1012cm-2的正极化电荷。该高密度固定正电荷可强烈补偿捕获电子后的表面态,从而抑制由表面态缓慢放电导致的电流坍塌。极性PEALD-AlN钝化显示出比传统PECVD-SiN钝化优秀的电流坍塌抑制能力。采用PEALD-AlN(接触层)/PECVD-SiN(覆盖保护层)复合钝化结构,在Si基GaN研制出600V低动态导通电阻耗尽型和增强型绝缘栅GaN功率开关器件,在Si基GaN上实现了E/D(增强型/耗尽型)器件单片集成。

CMOS工艺中LPCVD高温生长(>600℃)的SiN介质致密性好,击穿电压高,热稳定性良好,无等离子体表面损伤,在GaN基功率开关器件表面钝显示出良好潜力。采用LPCVD-SiN钝化在GaN基HEMT器件上有效提升了功率输出能力,同时推测该介质与(Al)GaN间的氧化层(约2nm)可能是器件仍存在电流崩塌的原因。将原位等离子体预处理引入LPCVD系统以有效去除该界面氧化层,进一步改善了LPCVD-SiN介质与(Al)GaN界面特性,抑制了绝缘栅GaN基功率开关器件的阈值漂移和电流坍塌。

3. 高绝缘栅介质

绝缘栅GaN基功率开关器件可靠性核心是高绝缘栅介质。良好的经时击穿(TDDB)特性是决定器件长期工作可靠性的关键因素,而介质中的正固定电荷直接影响增强型阈值的实现。

利用原子层沉积(ALD)技术制备的Al2O3是目前GaN基MIS-HEMTS中广泛采用的栅介质。但由于ALD装置中TMA(Al源)和H2O源的不充分反应,采用热模式ALD生长的Al2O3介质中含有一定量的Al-Al和Al-O-H等缺陷,它们被认为是栅氧介质中正固定电荷的来源,正电荷的存在会导致阈值电压的负向移动,阻碍了增强型的形成。近期研宄发现,采用活性较强的O3取代H2O作为ALD中的O源,不仅能使TMA被充分反应,而且能避免采用等离子O2源(等离子模式生长)所引入的表面轰击损伤等问题。实验发现,采用O3源生长的ALD-Al2O3击穿电场能达到8.5MV/cm,也具有良好的TDDB特性。最重要的是,O3有效抑制了栅介质中的正固定电荷,密度能控制在9×1011cm-2。在此基础上,通过介质后退火方法进一步降低了Al2O3/GaN界面正电荷,将绝缘栅GaN基MOS-HEMT阈值提髙到5.2V。

采用LPCVD方法高温制备的SiN介质具有良好的抗击穿和TDDB特性。LPCVD-SiN与GaN间的导带带阶为2.75eV,且自身的击穿场强达到13MV/cm,高于PECVD-SiN栅介质,故LPCVD-SiN栅介质是制备绝缘栅GaN基功率开关器件的理想选择,可极大扩展栅极的安全阚值范围。

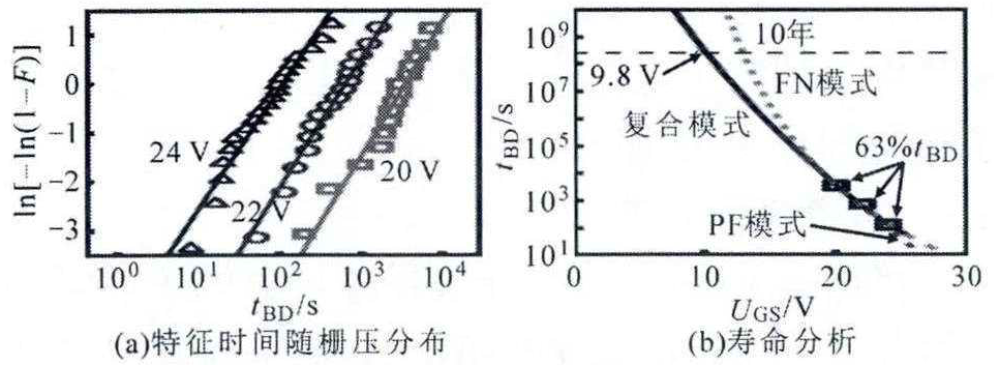

图5中,采用韦伯统计失效分析方法,LPCVD-SiN介质的韦伯斜率β=2.4,说明其TDDB特征时间tBD呈很好的一致性。以10年寿命为计量标准,63%失效率对应可承受栅压为9.8V。LPCVD-SiN介质在100℃和200℃高温下可靠性良好。为继续提升GaN基增强型MIS-HEMT中LPCVD-SiN栅介质的可靠性,在LPCVD-SiN与凹槽栅间插入一层低温生长的PECVD-SiN(约2nm),以有效保护栅区被刻蚀后的(Al)GaN表面(LPCVD的高温生长可能导致刻蚀GaN表面退化),从而制备出了阈值2.37V、击穿电压650V的高性能MIS-HEMT。其中该复合栅介质在栅压11V时TDDB=寿命超过10年,显示了LPCVD-SiN栅介质在绝缘栅GaN基功率开关器件中的良好可靠性。

图5 TDDB特征时间和寿命分析

同时开发了感应耦合等离子体CVD、原位金属有机化合物CVD等SiN栅介质生长方法,这些介质的TDDB特性还需继续验证。