1. 无金欧姆接触

传统GaN-on-Si功率器件欧姆接触主要采用Ti/Al/X/Au多层金属体系,其中X金属可为Ni,Mo,PT,Ti等。这种传统有Au欧姆接触通常采用高温退火工艺(>800℃),第1层Ti在常温下能与(Al)GaN反应,从而在(Al)GaN表面产生氮空位(浅施主),形成高掺杂n型层,促进电子的遂穿效应降低欧姆接触;第2层Al主要防止Ti与(Al)GaN的过度反应,起钳制作用;第3层的Ni是扩散阻挡层,防止Au过多向内部渗透;最外层的Au既是防氧化保护层,同时可与Ti,Al等在高温下形成低阻合金相,进一步降低接触电阻。目前传统有Au欧姆接触电阻通常能低至0.5Ω·mm以下。

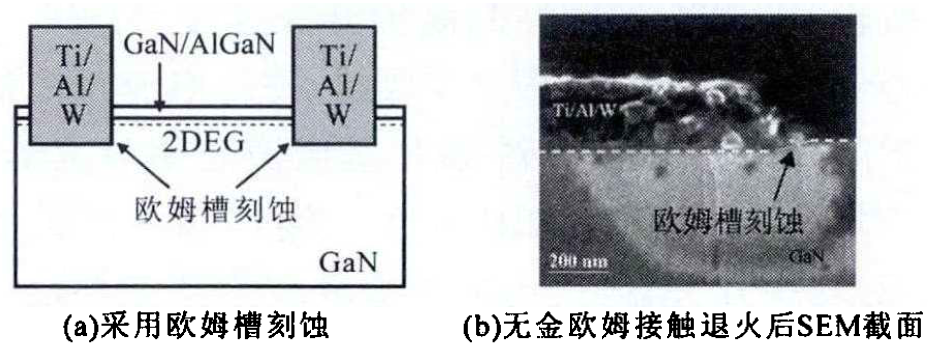

基于Ti/Al的金属体系是GaN基电子器件欧姆接触较成熟的工艺。因此,目前无Au工艺基本采用该技术。将Au换成Pt(即Ti/Al/Ni/PT),沿用高温工艺(975℃),实现接触电阻0.6Ω·mm,表面平整的欧姆性能。另一些学者将欧姆槽刻蚀引入到Ti/Al/W无金工艺中,如图1所示,在870℃条件下实现接触电阻低于0.5Ωmm。

图1 欧姆槽刻蚀引入Ti/Al/W无Au工艺原理图

鉴于LPCVD栅介质在绝缘栅器件中良好的可靠性,开发了针对此介质的先栅MIS-HEMT工艺。采用先栅的原因是在LPCVD高温腔体中,样品不能带有金属。采用BCl3/SF6进行2min欧姆前刻蚀减薄AlGaN势垒层,然后淀积Ti/Al/Ti/TiN,在550℃低温下退火实现(1.25±0.15)Ω·mm的接触电阻。该低温工艺有效保护了LPCVD栅介质/(Al)GaN界面,顺利实现了先栅工艺流程。在GaN-on-Si上优化了Ti/Al比,当比例为0.05时,接触电阻可降至0.62Ω·mm(550℃低温退火)。

2. 无金栅工艺

前述提到,栅介质/(Al)GaN界面态和栅介质绝缘特性直接决定了绝缘栅GaN功率开关器件的长期可靠性。作为栅极的重要组成部分,栅金属及其与栅介质的界面稳定性对栅极的TDDB甚至动态特性也具有不可忽视的影响。Ni,Al,W,半金属TiN及多晶Si是目前CMOS工艺中常用的几种材料。其中Ni是在传统有金Ni/Au栅工艺中去掉Au形成的,它与LPCVD-SiN和Al2O3都能形成良好的接触性能。Ni/Al2O3接触势垒达到2.9eV,它与LPCVD-SiN接触势垒介于1.85~2.3eV,均能有效抑制栅极的反向漏电。

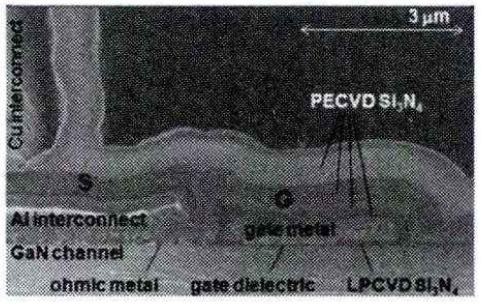

但由于Ni的干法刻蚀工艺难度较大(CMOS工艺通常采用干法刻蚀使金属图形化,而非lift-off剥离),故无金工艺中通常不采用Ni栅。在8英寸工艺中选用TiN作为栅金属接触层,采用干法刻蚀工艺能实现良好的图形化,如图2所示。

图2 MIS-HEMT器件截面SEM形貌

多晶Si栅是Si-CMOS中最常用的栅。将多晶Si栅与LPCVD-SiN钝化/栅介质结合,对比Al金属栅,显著提高了MIS-HEMT的栅极击穿和寿命,LPCVD-SiN栅介质厚度为20nm时,栅极击穿电荷达到714C/cm2。3. 绝缘栅Si基GaN功率开关产业化制备技术

F离子注入和凹槽栅是绝缘栅GaN-on-Si功率开关器件的主要制备技术。Si基AlGaN/GaN异质结构是平面工艺的主要外延结构,其中AlGaN势垒层的厚度通常只有约20nm。以凹槽栅工艺为例,为形成增强型通常要将势垒层刻蚀到6nm以下。故在进行离子注入或栅槽刻蚀时,注入/刻蚀深度及损伤控制是此类增强型技术的主要挑战。开发具有自截止注入/刻蚀特性的工艺或设计具有阻挡层的势垒层结构是实现单芯片增强型Si基GaN器件产业化制备的关键技术。

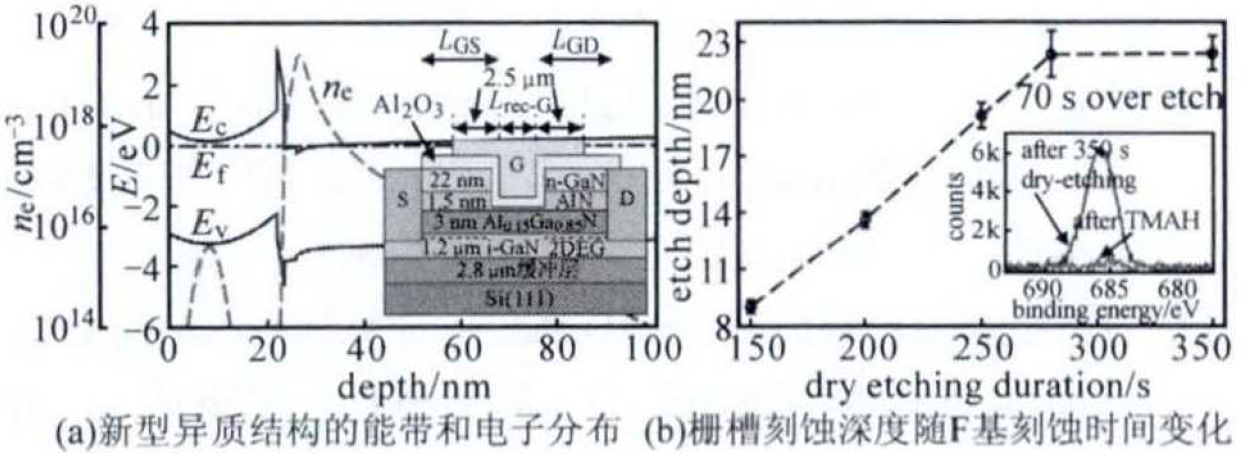

在UV光照条件下,采用K2S2O8和KOH混合腐蚀AlGaN势垒层制作凹槽栅,发现AlGaN/GaN间的AlN插入层能形成很好的自阻挡效应,显著提高了增强型器件阈值均匀性,阈值标准偏差低至177mV。同时设计了一种n-GaN(22nm)/AlN(1.5nm)/AlGaN(3nm)势垒层结构,见图3。利用F基等离子体与AlN反应生成的AlF3作为刻蚀阻挡层,制备出阈值0.3±0.04的增强型MIS-HEMT器件,栅沟道迁移率达1131cm2·V-1·s-1。

图3 nGaN/AlN/AlGaN势垒层结构参数

采用PECVD-SiO2作为硬掩膜,通过高温长时间O2退火实现栅区AlGaN势垒层的完全氧化(615℃,40min),然后KOH湿法去除被氧化的势垒层,淀积ALD-Al2O3栅介质,制备出基于AlGaN/GaN异质结构的增强型MOS-HEMT,器件阈值达3.2V。为进一步提高栅区沟道2DEG输运能力,采用双异质结GaN(2nm)Al0.26Ga0.74N(18nm)/AlN(1nm)/GaN(3nm)/Al0.2Ga0.74N(18nm)/AlN(1nm)/GaN,同时采用高温氧化在第2个GaN(3nm)层实现截止,器件栅区沟道迁移率达1400cm2·V-1·s-1(原始沟道2DEG迁移率为1700cm2·V-1·s-1),说明该自截止氧化腐蚀技术导致的2DEG输运能力退化很小。同时结合PEALD-AlN钝化,AlN界面插入层和AlGaN/AlN/GaN/AlN/GaN双异质结构,研制出阈值0.5V(ID=10µAmm),亚阈值摆幅72mV/dec,击穿电压超700V的GaN-on-Si MIS-HEMT器件,栅区2DEG沟道迁移率高达1801cm2·V-1·s-1)。上述说明双异质结自截止技术有望获得低导通电阻增强型GaN基MIS-HEMT器件。

图4 新型异质结构和MIS-HEMT器件结构

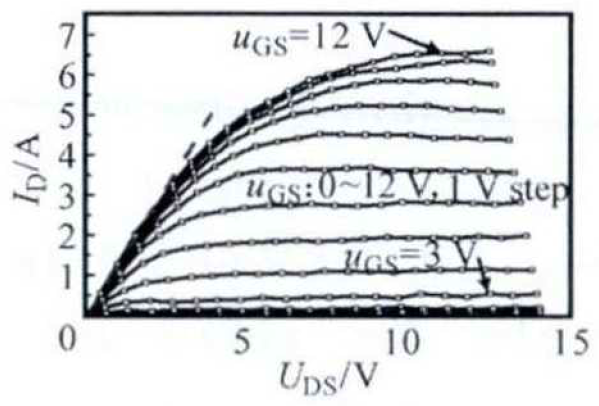

图5 GaN基MIS-HEMT器件I-U特性

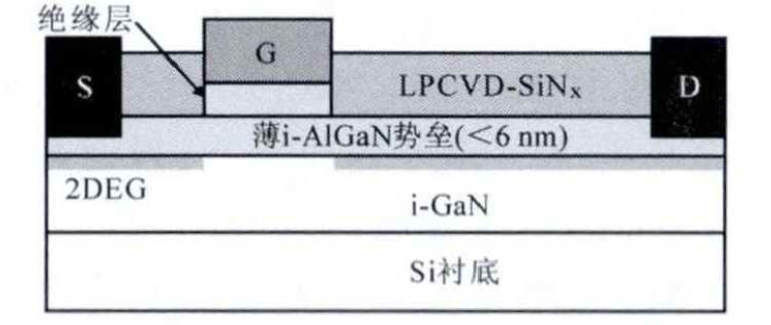

为进一步提升绝缘栅GaN基MIS/MOS-HEMT的良率和工艺重复性,利用MOCVD外延良好的厚度控制能力,在4英寸Si衬底上外延出超薄势垒AlGaN(<6nm)/GaN异质结构(本征增强型),再采用高温LPCVD-SiN钝化实现栅极以外2DEG的恢复,如图4所示。该技术利用LPCVD-SiN/(Al)GaN间的高密度(2.6×1013cm-2)正电荷,可将超薄势垒AlGaN/GaN异质结构的2DEG方阻降至350Ω/□以下,达到可与常规厚度AlGaN(约20nm)/GaN异质结构比拟的数值。同样利用MOCVD原位生长的in-situ SiN纯化同样在薄势垒上实现了2DEG的良好恢复,研制出具备良好击穿特性的增强型HEMT。该技术外延结构简单,优点是F基刻蚀LPCVD-SiN时能在AlGaN表面形成良好的截止,显著提高了阈值电压与沟道电阻的均一性。基于该技术研制出了20mm栅宽绝缘栅GaN增强型MIS-HEMT器件,导通电阻达0.75Ω,见图5。这种top-down工艺制程可有效促进绝缘栅GaN-on-Si MIS/MOS-HEMT器件的产业化制备。