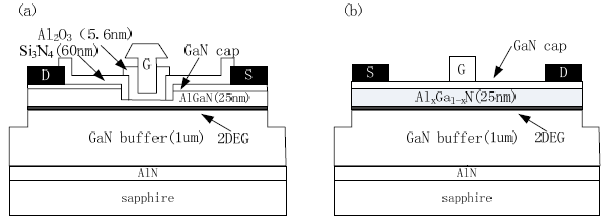

图1 凹槽栅MOS-HEMTs器件和常规GaN HEMTs器件的结构图

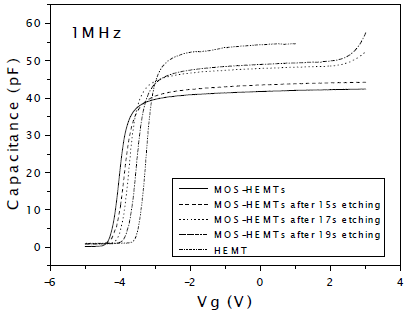

从CV特性分析凹槽栅深度和栅介质的特性。CV测试图形采用的圆环结构,外圆环是欧姆接触(Ti/Al/Ni/Au,厚度为220/1400/550/450Å),经过870℃高温退火40s形成。圆环内部为肖特基接触(Ni/Au/Ni=450/2000/200Å),半径为65um。测试频率为1MHz,栅压从-5V扫到3V,步长为0.1V。

图2 不同刻蚀时间的MOS-HEMTs器件的CV特性

如图2所示,CMOS-HEMT为常规MOS-HEMTs电容结构中的零偏电容,其值为42.4pF,CHEM为HEMTs电容结构中的零偏电容,其值为54.4pF,A为CV测试面积,Cox为Al2O3的相对介电常数,dox为栅介质的厚度,εox为介质层的电容,ε0为真空条件下的介电常数。从以上这三个公式可算出栅介质Al2O3的厚度为5.52nm,这比计划生长的5nm厚,可能是材料表面形成一层低介电常数氧化层的缘故。由公式(2)计算得出势垒层厚度为19.3nm。同样利用这几个公式可以计算出刻蚀15s,17s和19s行成的凹槽栅深度分别为0.62nm,2.71nm和3.25nm。

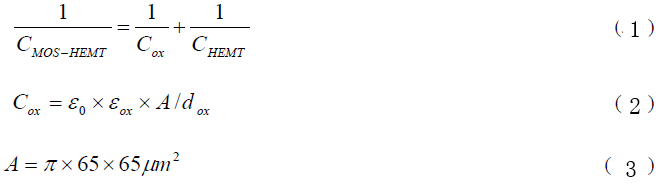

从图3可以看出,随着刻蚀时间的增加,刻蚀深度并不是线性的,这有两个原因:a、RIE刻蚀需要起辉时间;b、势垒层表面有层自然氧化层,并且不致密。另外,阈值电压负漂的影响随着刻蚀时间的增加,随之减小,这说明凹槽栅刻蚀能够有效地减弱MOS结构带入的阈值电压负漂的影响。

图3 不同凹槽栅深度MOS-HEMTs随着刻蚀时间的阈值电压漂移量和势垒层层厚度的对比。

根据测的1MHz下的CV特性曲线,根据公式(4)和(5)

图4 不同凹槽栅深度的MOS-HEMTs的载流子浓度分布。

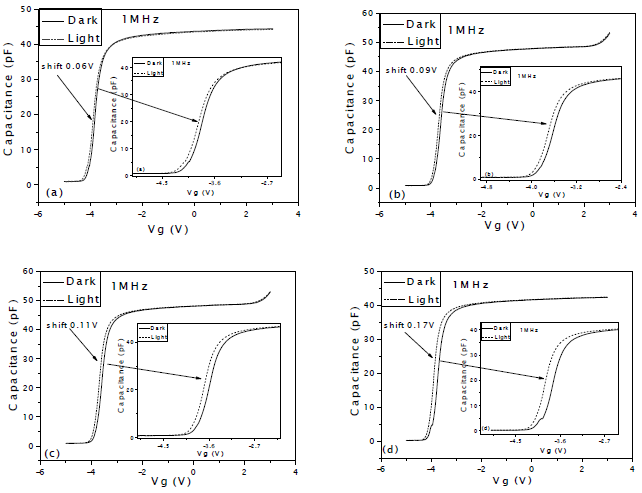

光照CV法是计算和评价AlGaN/GaNMOS-HEMTs器件MOS电容介质层中和MOS结构与AlGaN势垒层的界面态特性的重要方法。通过黑暗环境下测试,栅电压从3V扫到-5V,让二维电子气从积累到耗尽,然后再对器件光照,让俘获的电子从陷阱中释放出来,栅电压从-5V扫到3V。从图5可看出,通过黑暗和光照条件下得到的CV曲线有所漂移,这是由于陷阱俘获电子的缘故,这便可估算出MOS结构中的界面态密度。我们认为这种平带电压的漂移是由于界面陷阱俘获电子导致的,所以可通过△Q=C△V和Ns=△Q/qA计算出四种MOS结构中的界面态密度,凹槽栅深度为0.62nm的MOS-HEMTs器件的界面态密度为4.69×1011cm-2eV-1,凹槽栅深度为2.71nm的MOS-HEMTs器件的界面态密度为7.03×1011cm-2eV-1,凹槽栅深度为3.25nm的MOS-HEMTs器件的界面态密度为8.59×1011cm-2eV-1,而常规MOS-HEMTs器件的为1.33×1012cm-2eV-1。不难看出,通过凹槽栅刻蚀后,MOS结构的界面态密度减小了一个量级,说明凹槽栅刻蚀确实能够有效地减小MOS栅介质和AlGaN势垒层间的界面态密度。另外随着凹槽栅刻蚀深度的增加,界面态密度有所增加,这可能是由于刻蚀损伤所造成的。

图5 (a)0.62nm深的凹槽栅MOS-HEMTs; (b)2.71nm深的凹槽栅MOS-HEMTs;

(c)3.25nm深的凹槽栅MOS-HEMTs; (d)常规MOS-HEMTs的光照CV法测试图。

(c)3.25nm深的凹槽栅MOS-HEMTs; (d)常规MOS-HEMTs的光照CV法测试图。

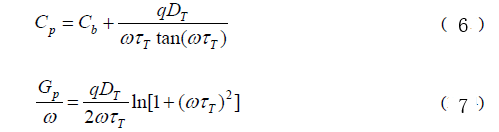

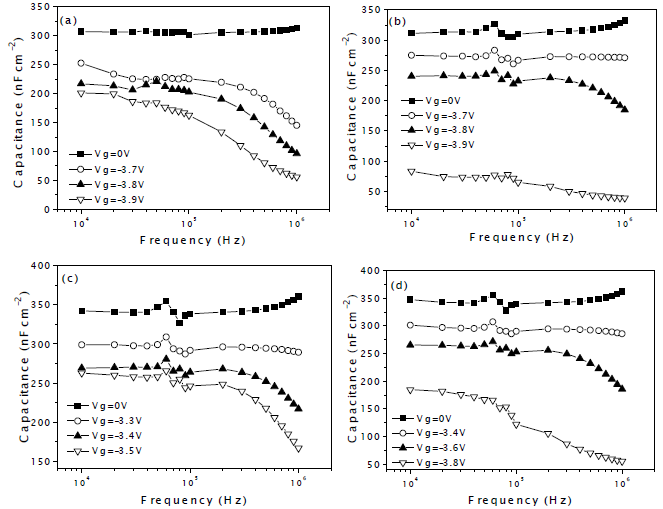

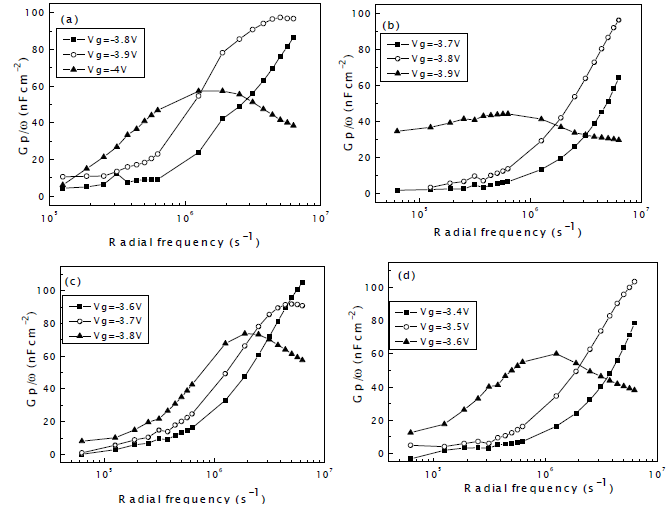

为了分析不同槽栅结构MOS-HEMTs的陷阱特性,我们比较了常规结构MOS-HEMT和槽栅结构MOS-HEMT器件的电导随频率的变化关系。变频C-V测试采用keithley4200scs,测量频率从10KHz到1MHz,步长为10KHz。根据以下公式:

其中,DT为陷阱密度,τT为陷阱时常数,Cb为势垒层电容,ω为角频率。可通过拟合实验所得的CP(ω)或GP(ω)数据来获得陷阱密度和时常数。不同槽栅深度的MOS-HEMTs的CP(ω)随ω的关系是在阈值电压附近偏压所测的,如图6所示。通过图7,我们得到了常规MOS-HEMT结构的界面态密度Dit=(0.72-1.22)×1012cm-2eV-1,界面态时常数为τit=(0.19-0.64)μs;而0.62nm深的凹槽栅MOS的界面态密度Dit=(0.55-1.08)×1012cm-2eV-1,界面态时常数为τit=(0.2-1.59)μs;2.71nm深的凹槽栅MOS的界面态密度Dit=(0.97-1.14)×1012cm-2eV-1,界面态时常数为τit=(0.24-0.49)μs;3.25nm深的凹槽栅MOS的界面态密度Dit=(0.76-1.2)×1012cm-2eV-1,界面态时常数为τit=(0.19-0.94)μs。可以看出经过凹槽栅刻蚀后,界面态密度没有增加,反而有明显的减小,对比界面态时常数的变化,可以看出界面态时常数的量级都在微秒级别,属于快态陷阱,这说明槽栅结构能够减少Al2O3栅介质与势垒层之间的表面态密度,且不会产生新的界面态陷阱类型。因为暴露空气中的材料表面会有一层自然氧化层,在AlGaN亚表面区域会由于AlOx和GaOx氧化物的产生使得N原子的缺失,从而形成了N空位,同时亚表面区域也有其他杂质(如C,O,Si等)。通过Cl基刻蚀这层氧化层减小了栅下区域界面态密度,而小功率刻蚀不产生新的界面陷阱类型。

图6 (a)0.62nm深的凹槽栅MOS-HEMTs;(b)2.71nm深的凹槽栅MOS-HEMTs;

(c)3.25nm深的凹槽栅MOS-HEMTs; (d)常规MOS-HEMTs的电容与测试频率的关系图。

(c)3.25nm深的凹槽栅MOS-HEMTs; (d)常规MOS-HEMTs的电容与测试频率的关系图。

图7 (a)0.62nm深的凹槽栅MOS-HEMTs; (b)2.71nm深的凹槽栅MOS-HEMTs;

(c)3.25nm深的凹槽栅MOS-HEMTs; (d)常规MOS-HEMTs的电导与测试频率的关系图。

(c)3.25nm深的凹槽栅MOS-HEMTs; (d)常规MOS-HEMTs的电导与测试频率的关系图。