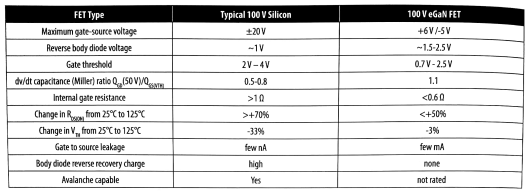

表1展示了氮化镓场效应晶体管与功率MOSFET进行比较的一些重要参数。

表1 100V硅MOSFET器件与100V氮化镓场效应晶体管器件的参数比较

栅极驱动的下拉电阻

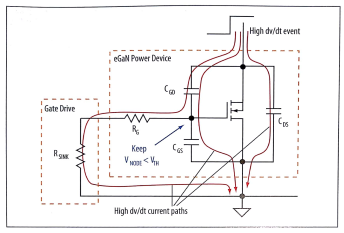

氮化镓场效应晶体管优势之一是其高开关速度。然而,随这个优势而来的间题是出现更高di/dt和dv/dt,这不仅要求版图具有更小的寄生电容、电阻和电感,也需要对栅极驱动有新的考虑。为了对此有进一步的了解,我们将探讨一个半桥电路,它使用一个互补式器件,具高导通dv/dt,如图1所示。

米勒电荷的电流从漏极经过CGD和CGS至源极,以及通过CGD至内部的栅极电阻(RG)及栅极驱动器吸收电阻(RSink)再至源极。避免这个器件的dv/dt(米勒)导通可从以下的等式1得出:

CGDxdv/dtx(RG+RSink)x(1-e-dt/a)<VTH (1)

其中a代表无源网络的时间常数(RG+RSink)x(CGD+CGS)。而dt是dv/dt的开关时间。为了避免氮化镓场效应晶体管的米勒导通,我们需要限制器件的栅极与源极之间的总路径电阻(RG+RSink)。如果器件具有良好的米勒比率(即QGD/QGSx(VTH)<1),这个要求将不需要。可是,实际上QGD会随VDS而增加,所以这个比率也将随更高的漏极至源极的电压而变差,因此可以导致米勒导通。在另一方面,在很低的总线电压情况下的QGD/ QGSx VTH的值会远小于1,从而改善公式(1)的数值。为了安全起见,在使用更高电压的器件时,我们推荐使用0.5欧姆或以下的栅极驱动的下拉电阻。

图1 当器件处于关断状态时,dv/dt对器件的影响及避免米勒导通的要求。

栅极上拉电阻

由于氮化镓场效应晶体管的总米勒电荷(QGD)远小于具等同导通电阻的功率MOSFET,因此前者的开关速度有可能比后者快很多。在“硬”开关的转换期间,太高的dv/dt会形成导通而降低效率。因此最好是可以调整器件的栅极驱动的上拉电阻,使其在转换时不会引致其它不必要的损耗,并同时调整开关节点电压的过冲和振铃现象来改善器件受电磁干扰(EMI)的性能。这一点,在使用功率MOSFET的应用中,可以在串联栅极驱动输出端使用一个电阻和反并联二极管来实现。在使用氮化镓场效应晶体管的应用,由于氮化镓器件具低阈值电压,我们不推荐这个方法,而是采用最简单的通用解决方案,把驱动器的栅极上拉和下拉的连接分开及插入一个分立电阻。

栅极驱动的死区时间

氮化镓场效应晶体管的反向偏置或体二极管的操作具有无反向恢复损耗的优点。但这个优点被更高的体二极管正向压降所抵消,因为二极管的传导损耗可以很大,特别是在低电压和高频率的情况下。与硅二极管的反向恢复损耗不同,我们可以通过死区时间管理,最大限度地减小体二极管的导通时距。氮化镓场效应晶体管具有短并且小变化的开关时间,我们因此可以精密控制死区时间,把传导损耗降至最低。将死区时间降至几纳秒实际上可以避免体二极管损耗。

栅极驱动的电源调整

目前的氮化镓场效应晶体管最大的栅极电压是6V,这会限制栅极驱动的电源范围,并需要进行若干的电源调整。

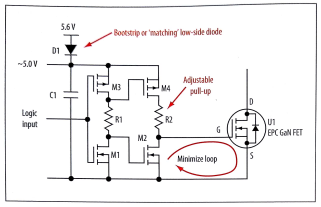

我们最关注的是在一个半桥配置的浮动或高边电源。如果想以一种简单方法使低边(以接地为基准)和高边电源电压更为匹配,我们可以在一个分立栅极驱动器使用一个“匹配二极管”,如图2所示。

图2 氮化镓场效应品体管的分立栅极驱动器的解决方案,显示匹配互补式高边及低边驱动器的电源电压的方法

这种做法只适合应用于半桥应用的互补式开关,因为它的死区时间和体二极管导通值是最小的。如果在应用中的氮化镓体二极管的导通时间显著比自举二极管的导通时间为长,2V的体二极管压降将施加在电源电压上,这个可以导致高边电源出现过压的情况,并需要使用后自举的稳压电源来解决。

一个基于氮化镓场效应晶体管而优化的100V半桥栅极驱动器,可实现自举的稳压电源调节。集成在非锁存欠压闭锁(UVLO)上的是一个保护过压的器件,限制自举电压在5.2V,确保器件在所有电路的条件下仍然可以可靠地工作。除了过压保护器件外,为发挥氮化镓场效应晶体管的最佳效率,我们使用独立的源极及漏极引脚,具有大于50V/ns dv/dt性能、匹配的传播延迟、0.5欧姆下拉栅极驱动电阻,以及独立的高边和低边输入端。