我们根据上述不同的考虑因素推荐三个使用氮化镓场效应晶体管的印刷电路板的版图,每一个版图皆提供更高的性能基准:

1)具单面端子的版图,适合于两层或以上的多层板设计;

2)具双面端子的版图,适合于四层或以上的多层板设计;

3)具填孔、双面端子的版图,适合于需要最低共源电感的设计。

具单面端子的印刷电路板的版图

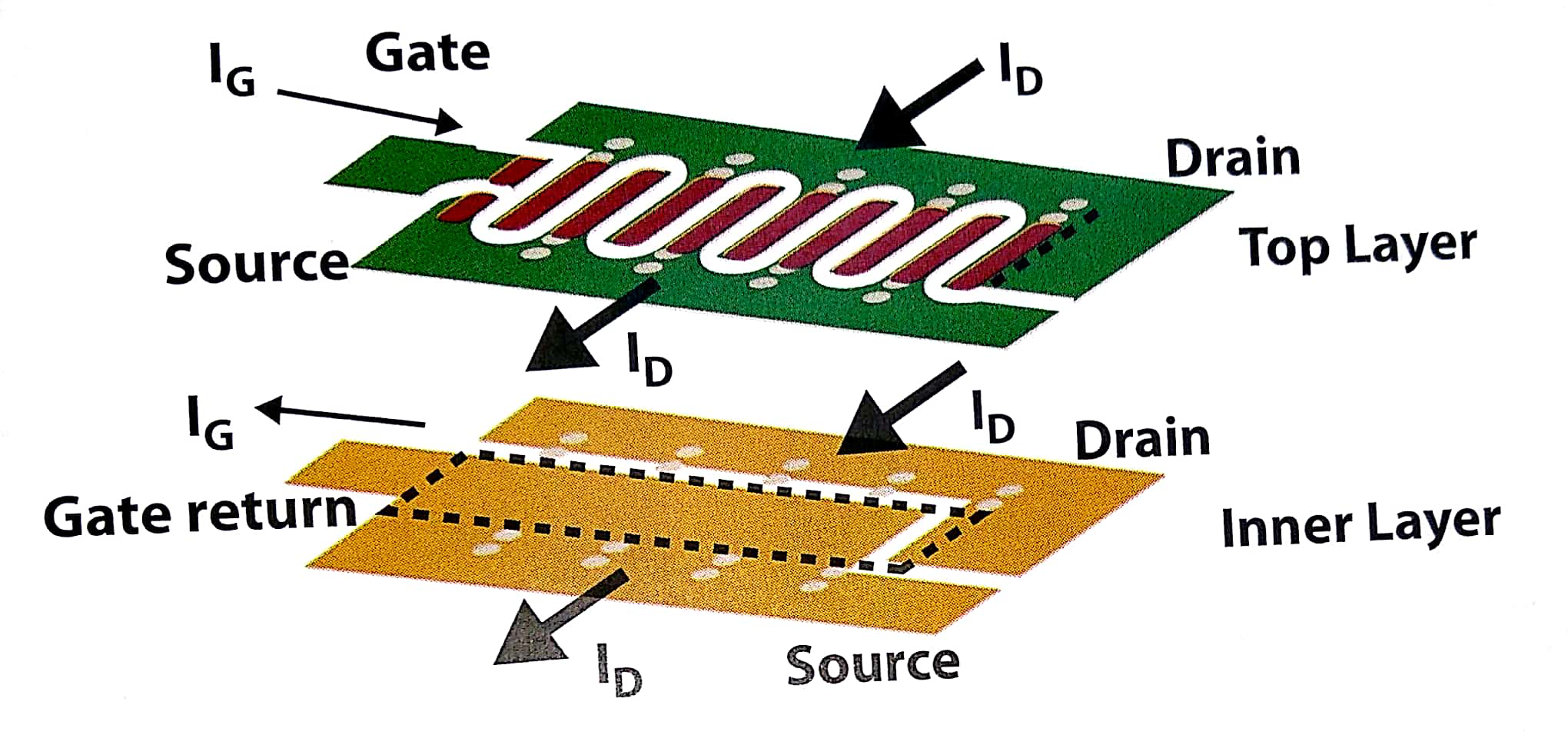

当成本是设计的一个重要考虑因素时,我们推荐单面端子的版图设计。也可以用于双层或双层以上的印刷电路板的设计,如图1所示。我们可以把电源连线至漏极和源极的版图放置在电路板的同一层上,并端接于场效应晶体管的一边。我们建议使用通孔将漏极和源极的端子连接到额外的数层,以进一步增强器件的载流能力。推荐的通孔设计是具10密耳(254微米)的通孔直径和20密耳(508微米)的环孔直径。推荐每个焊盘有两个通孔,并且要有足够的间距,以符合电路板的设计指南所提供的值,及共源电感极限的要求。为了进一步减少共源电感,我们建议在顶层(晶片的焊盘层)的下一层放置一层铜制的平面,并连接到源极。这个源极的平面用作为传输主电流和栅极回路的电源平面,此平面在图1中显示为金色。设计师想进一步减少栅极至源极电路和漏极至源极电路之间的耦合,可以把两个电路的电流设计为正交走向。使用厚度最少是两盎司的铜层,可确保电路板具有最低的连接阻抗。

我们推荐40V及100V的低压器件的焊盘使用小线宽及小线距,工程师可能需要咨询电路板的生产商,以确定他们所提供可选的规格与设计的要求相符。一般来说,选用一盎司铜的厚度的电路板将符合大部分印刷电路板生产商可允许的误差范围。

图1 具单面端子版图的结构的例子

具双面端子的印刷电路板的版图

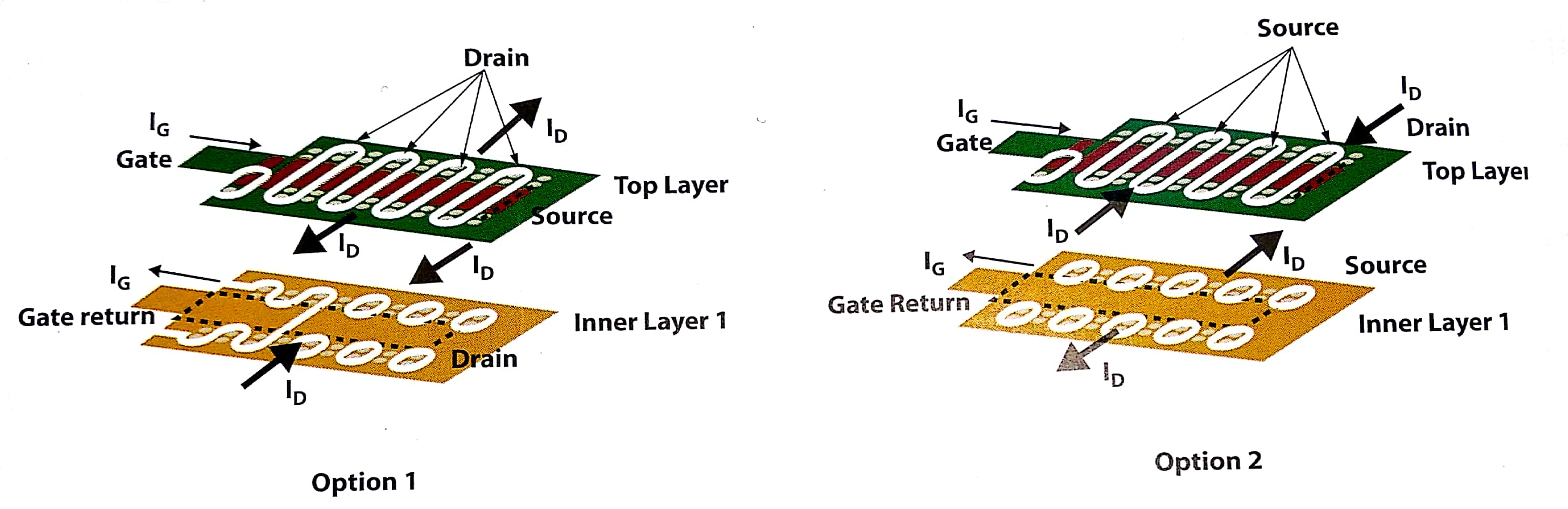

当性能和成本是设计的重要考虑因素时,我们推荐使用具双面端子的电路板设计,这种设计可以应用于具四层或四层以上的电路板,这种版图的两个例子见图2。第一个可选的版图是源极端子放在顶(焊盘)层,面漏极端子在它的下一层。第二个可选的版图是漏极端子在顶(焊盘)层,而源极连接点在它的下一层。电源分别在电路板的各层连接到漏极及源极,止于在晶片两面的端子,如图2所示。我们推荐漏极及源极端子通过通孔连接至额外的多层板,以增加器件的载流能力。对于40V及100V的低压器件来说,理想的钻孔的直径是6密耳(152微米),而孔环的直径是8密耳(203微米)。对200V的中压器件而言,理想的钻孔的直径是8密耳(203微米),而孔环的直径是12密耳(304.8微米)。我们推荐焊盘的每一面有两个通孔,它们的间距应该根据电路板设计指南及共源电感的限制而设定。本设计将通孔聚集在一起,并使它们相互靠近,而设计师需要交错排列通孔,这可以避免在印刷电路板上形成撕裂区。另外的选择是要求电路板的制造商将电路板的纤维翾粒旋转45度,但这将增加电路板的成本。

为了进一步减少共源电感,我们建议在顶层(晶片的焊盘层)的下一层放置一层铜制的平面,并把它连接至栅极-源极回路。如果想进一步减少栅极至源极电路和漏极至源椴电路之间的耦合,设计工程师师可以把两个电路的电流设计为正交走向。如图2所示。如果每一层的铜的厚度最少是两盎司,可确保电路板具有最低的连接阻抗。我们只需要在一层板设计栅极回路,把其它各层的位置留给大电流平面使用。

图2 具双面端子版图的结构的例子,有两个选择给每一层的配置。

具双面端的填孔端子的版图

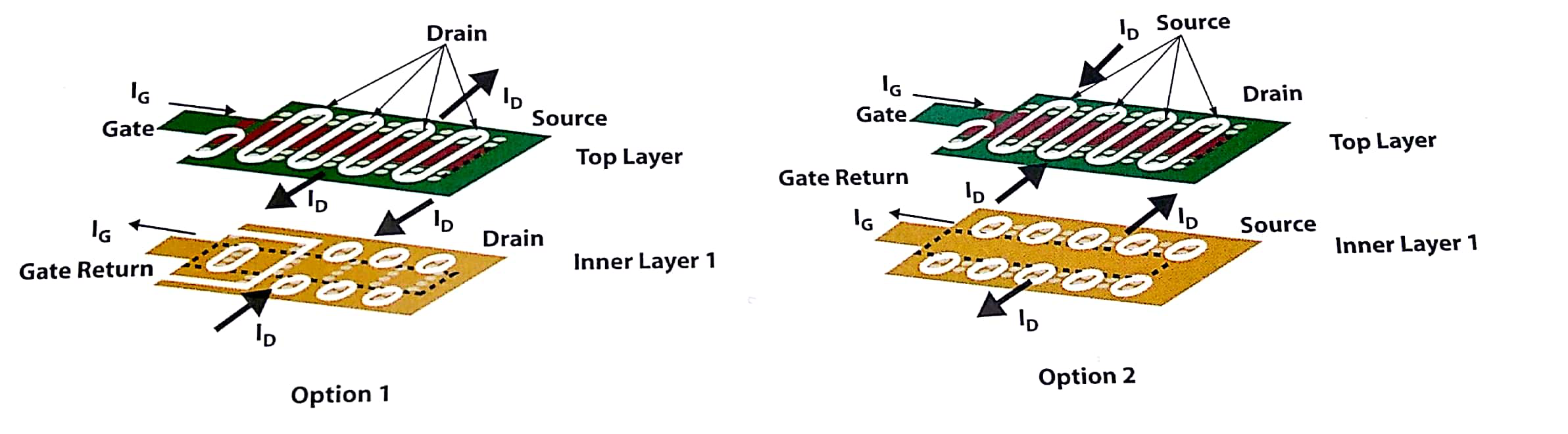

当性能是设计的重要考虑因素时,我们推荐使用具双面端的填孔端子的电路板设计,这种设计可以应用于四层或四层以上的电路板,这种版图的两个例子见图3。第一个可选的版图是把源极端子放在顶(焊盘)层,而漏极端子在它的下一层。第二个可选的版图是把漏极端了放在顶(焊盘)层,而源极连接点在它的下一层。电源分别在电路板的各层连接到漏极及源极,止于在晶片两面的端子,如图3所示。我们推荐漏极及源极端子通过通孔连接至额外的电路板层,以增加器件的载流能力。对于40V及100V的低压器件来说,理想的钻孔的直径是6密耳(152微米),而孔环的直径是8密耳(203微米)。对200V的中压器件而言,理想的钻孔的直径是8密耳(203微米),而孔环的直径是12密耳(304.8微米)。我们推荐焊盘的每一面有两个通孔,它们的间距应该根据电路板设计指南及共源电感的限制而设定。本设计将通孔聚集在一起,并使它们相互靠近,而设计师需要交错排列通孔,这可以避免在印刷电路板上形成撕裂区。晶片的焊盘区域的通孔需要具微小的尺寸,填孔的直径是6密耳(152微米),而孔环的直径是8密耳(203微米),并没有超过焊盘宽度及必须以非导电性或导电性的填充物料来填充,这可能增加成本。位于源极、栅极或漏极的焊锡棒下面空的通孔,会导致晶片跟电路板的相隔距离有很大的变化。这个间距变化可以1)影响使用者能否把场效应晶体管与电路板之间的空间清洁干净;2)增加晶片倾斜变化;及3)减低晶体管的温度循环性能。

为了进一步减少共源电感,我们建议在顶层(晶片的焊盘层)的下一层放置一层铜制的平面,并把它连接至栅极-源极回路。如果想进一步减少栅极至源极电路和漏极至源极电路之间的耦合,设计师可以把两个电路的电流设计为正交走向,如图3所示。使用厚度最少是两盎司的铜板,可确保电路板具有最低的连接阻抗。我们只需要在一层设计栅极回路,把其它各层的位置留给大电流平面使用。

图3 具双面端子、填孔版图的结构的例子,有两个选择给每一层的配置。

给相互连接器件使用的印刷电路板的版图

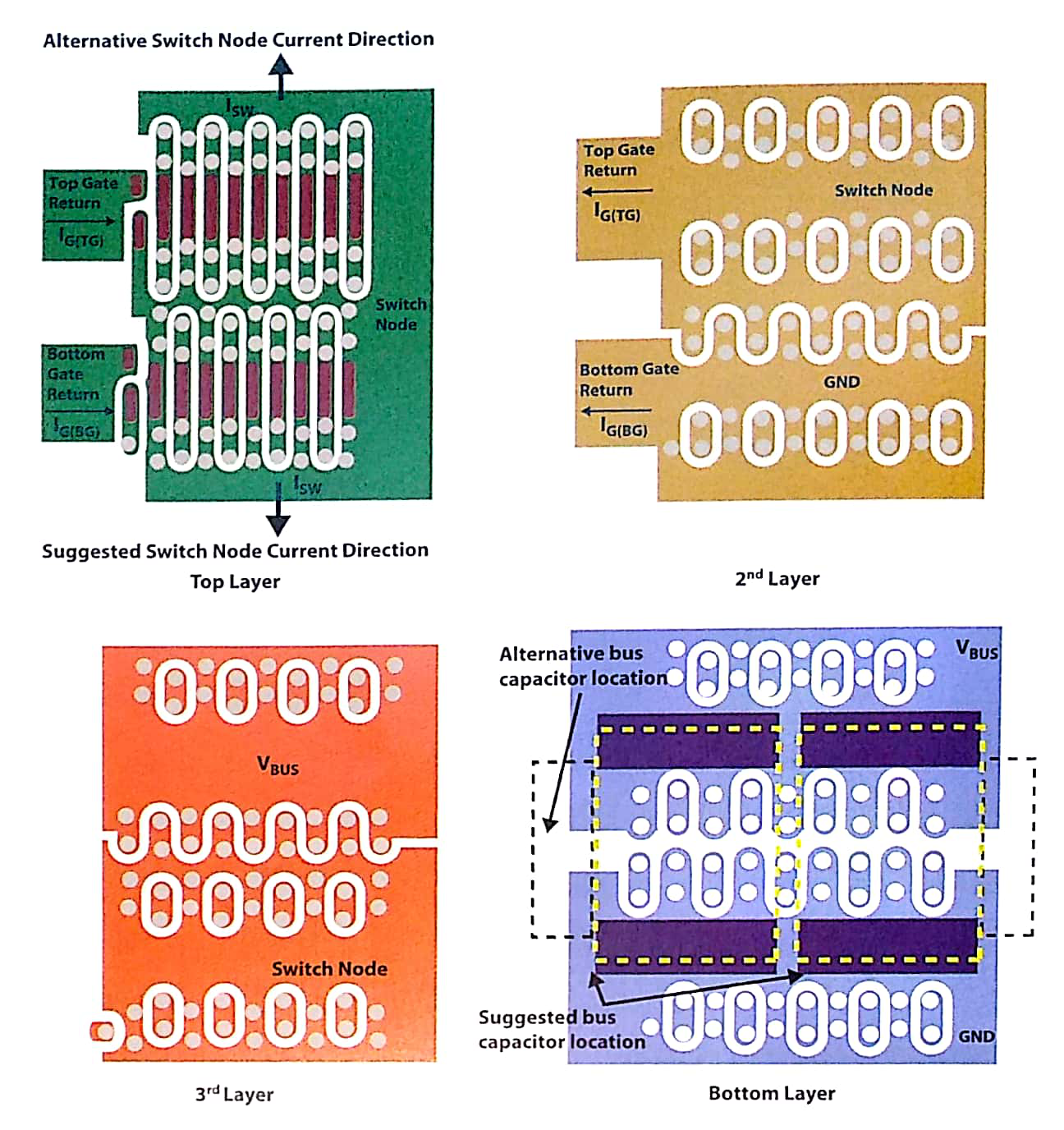

半桥拓扑的设计需要把器件连接在一起,如果需要在一个四层电路板的版图上把两个器件连接,我们推荐的方法如图4所示。铜层的厚度需要最厚,以降低电阻所引致的损耗及改善热量的散布(我们推荐外层皆使用两盎司铜)。从这个版图的例子,我们看到每个器件的源极连接都是以电场屏蔽从底下引出来(尤其是在器件的栅极结构下面可以最大限度地减少额外的寄生栅极漏电容(CGD)。我们将每个源极连接,通过第二层连接至现在的双屏蔽层,作为栅极驱动回路路径。而漏极则通过第三层连接及引出。我们需要折衷的是,要想达到更低的共源电感和整体的版图电感,在几何结构上我们需要增加寄生电容——特别是输出电容(CDS)——这是因为仍然需要最大限度地减小栅极至漏极的寄生电容(CGD)。主要总线的解耦电容可以位于一对器件的下面,或放在一边(见图4),并尽量使它们相互靠近,以最大限度地减少环路电感。栅极驱动器的输出端需要尽量靠近各个场效应晶体管的栅极位置。此外,把所有场效应晶体管长的一边拼在一起,以进一步减少器件与器件之间的电感。

图4 使用四层多层板版图的半桥版图的例子