传统对称的两路DPA从理论上来讲回退点的效率和峰值处的效率相同,但是由于在低功率工作时,峰值功放无法做到完全开路,会有功率泄露,所以实际回退后的效率低于峰值功放效率。对载波功放、峰值功放的输入功率和栅极偏压进行合理的配置,可以实现功率回退点效率的提高。文中提出的回退效率空间有助于Doherty功放的调试,在相同的回退效率下,功率配比和栅压可以有不同的配置方式,从而为DPA提供了参照和便利。

1. 高效Doherty功放理论分析

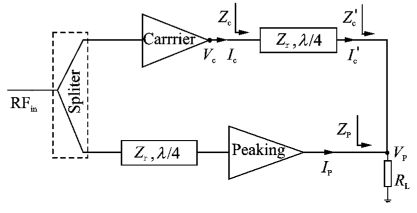

Doherty功放的原理图如图1所示。上下两路功放分别称为载波功放和峰值功放,输入端有等功率分配的功分网络馈电、四分之一波长传输线可实现阻抗变换、相位调整和输出功率合成等功能。

图1 DPA原理图

1.1 有源负载调制

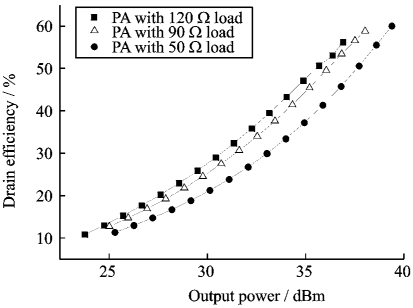

对于Doherty功放,当输入功率变化时,峰值功放的电流会发生变化,从而对载波功放造成“牵引”,使得载波功放的输出阻抗发生改变,更进一步而言,会对整个Doherty功放的效率产生影响,这即为“有源负载调制”现象。为此,采用Cree GaN CGH40010F设计了一个工作在2.25GHz输出功率10W的功放,来对DPA中峰值功放的负载调制效果进行验证。首先,将晶体管的最优阻抗Ropt匹配到50Ω,随后通过调相线和调整终端负载阻抗的值进行调整,分别将晶体管输出匹配到90Ω和120Ω。图2给出了一个AB类功放在不同负载阻

抗的条件下的效率曲线,可以反映负载调制带来的结果。

图2 AB类功放50、90、120Ω负载阻抗下的效率值

由图2可知,随着负载阻抗的增加,漏极效率随输出功率变化的曲线左移。也就是说,同效率下,高阻抗对应的输出功率更低;同输出功率下,高阻抗负载对应的效率更高。当输出功率从最大效率对应的39dBm回退到35dBm时,120Ω负载阻抗对应的效率曲线要明显高于90Ω和50Ω负载阻抗对应的效率曲线。由此可知,由于输出功率降低带来的效率损失可以通过适当提高负载阻抗加以补偿,适当的提高负载阻抗可以提高低功率区域的效率,“有源负载调制”的原理正是如此。

1.2 阻抗旋转与相位平衡

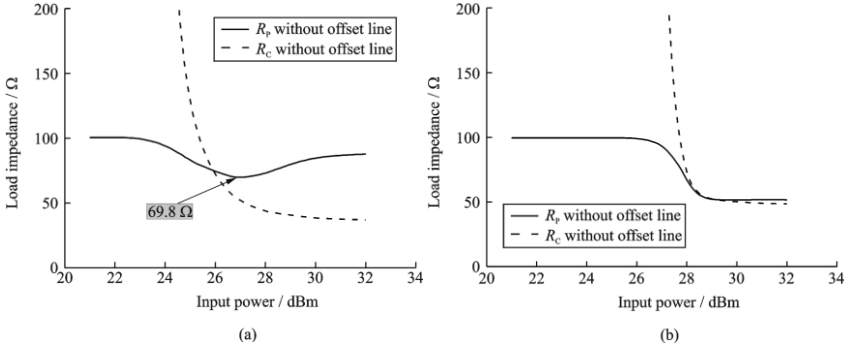

DPA工作过程中,载波功放和峰值功放所对应的阻抗值会有规律地变化,在阻抗的调整过程中,需要引入λ/4延迟线。图3给出了本文设计的DPA单元功放的动态负载阻抗变化曲线。

在图3中,Rc为载波功放的输出阻抗,Rp为峰值功放的输出阻抗。图3(a)显示,在未加入延迟线进行阻抗调节时,载波功放的输出阻抗最低只能被变换到69.8Ω,并且从该极点之后,负载阻抗随着功率的提升有上升的趋势,这就失去了“负载调制”的意义。图3(b)为在载波功放和峰值功放输出匹配电路之后加入了特定长度的延迟线后负载阻抗在圆图上旋转的结果。可以看出,随着输入功率的增大,载波功放的负载从100Ω渐变到50Ω,而峰值功放的负载阻抗从较大值(载波功放不开启)逐渐过渡到50Ω,载波功放和峰值功放的阻抗都与传输特性阻抗匹配。由此可见,延迟线可以很好地实现阻抗和相位的调节。

图3 载波功放和峰值功放的动态负载阻抗:(a)未加入相位延迟线;(b)加入相位延迟线

2. 功放设计与仿真分析

DPA的两个单元功放设计时兼顾了效率和输出功率,其中,载波功放的静态电流为68mA,处于AB类工作状态,峰值功放的栅极偏压调整为合适的值,使其在输出功率回退6dB的位置开启。借助ADS和HFSS仿真软件,基于Cree GaN CGH40010F的大信号非线性模型进行仿真校验,分析单元功放以及Doherty功放的工作特性。

非线性的栅漏电容(Cgd)和非线性漏源输出电容(Cds)是导致GaN器件发生AM/PM转换的因素,且Cgd发挥主要作用。减小Cgd和Cds的影响可以有效降低AM/PM效应。本文的DPA设计时,考虑了Cds的影响,将其纳入了输出匹配电路参与匹配,而未考虑非线性电容Cgd的影响。

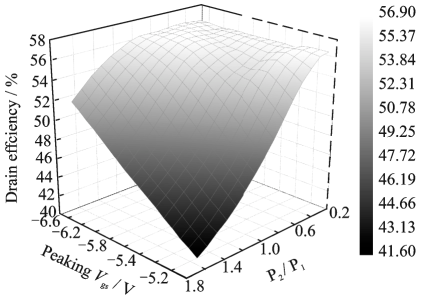

2.1 回退效率空间

影响DPA峰值功放开启时间的因素主要有两种:其一为峰值功放的栅偏压,其二为两路功放的功率配比。在相同的回退效率条件下,会出现不同的栅压和功率配置方案。对不同的方案进行探讨并结合功率回退点的效率,在三维空间形成一个“回退效率空间”。基于效率要求,在效率空间中选择合适的位置和对应的栅偏压与功率配比值,可以作为Do-herty功放设计的参照。

图4给出了本文设计的DPA的6dB的“回退效率空间”,其中,P2/P1代表峰值功放和载波功放的输入功率比,Vgs为峰值功放的栅偏压,纵轴代表从饱和点回退6dB时的漏极效率。可以看出,适当降低栅偏压或减小峰值功放和载波功放的功率配比均可以提高回退点的效率。但是这两个值都不能过大,栅偏压过大会使得峰值功放输出功率过低,无法实现良好的“负载调制”;功率配比过大会导致载波功放过饱和,线性度发生恶化。图4中的白色区域为回退点效率高于55%的区域,灰白色区域为50%~55%的区域,调整功放使得效率落入这些区域较为合适。

图4 DPA输出功率回退6dB的效率空间

2.2 对称DPA仿真

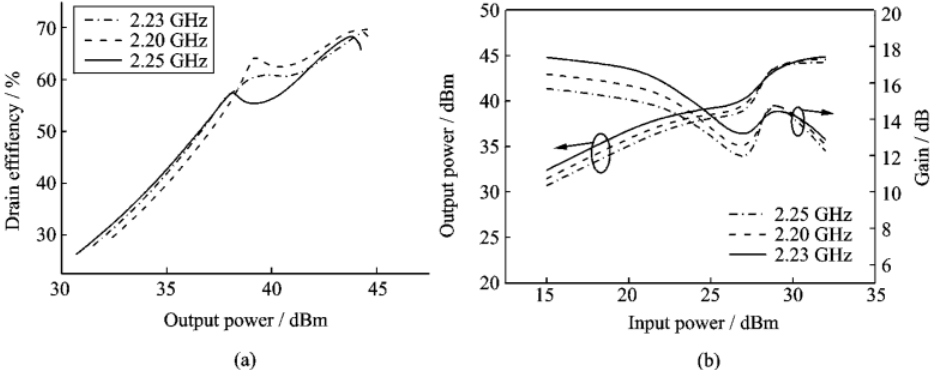

单音信号对功率分配比为1:1的Doherty功放的仿真结果如图5所示,在2.2GHz下,DPA在饱和点的漏极效率为69.6%,第二个效率峰值出现在从最大效率点输出功率回退5.6dB的位置,达到64.3%;在2.23GHz下,最大效率达到68.3%,输出功率回退4.8dB时达到第二个效率极值60.9%;在2.25GHz下,最大效率达到68.3%,回退6dB出现另一个效率极值,为57.5%。从图5中还可以看出,三种频率下的饱和输出功率均能达到44dBm以上,在2.20~2.25GHz频带内,功率增益在10dB以上。

图5 2.20、2.23、2.25GHz下Doherty功放:(a)漏极效率;(b)输出功率和增益曲线

3. 电路实现和测试结果

为了验证设计的准确性,对设计的DPA进行了加工和测试。采用的介质基板为Rogers RO4003,其相对介电常数为εr=3.55,厚度h=0.508mm,微带线铜箔厚度为0.035mm。功放管采用Cree公司的GaN CGH40010F。

对于AB类载波功放,采用了高低阻抗线实现了从最优阻抗Ropt=40Ω到传输线特性阻抗的匹配,采用并联单枝节对二次谐波进行了短路。对于C类峰值功放,与载波功放的设计思路基本一致,对基波和二次谐波进行了匹配。对三次以及以上的谐波为加匹配。输入匹配电路以最优效率为基准进行调谐,采用高低阻抗变换结构实现。直流偏置电路采用λ/4短接电容滤波电路组成。设计了等功率分配的Wilkinson功分器对载波功放和峰值功放进行驱动,输出端以“T形”结实现了两路功率的合成。

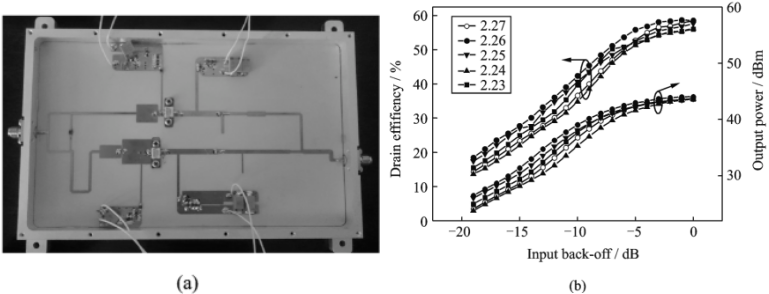

载波功放的栅极电压为-3V,峰值功放的栅极电压为-5.9V,漏极电压均为28V,两路功放的功率配比为1:1,测试时还需要加入驱动功放和衰减器等装置。功放的实物图如图6(a)所示。

对实物在不同频率下进行了测试,测试结果如图6(b)所示,在2.20~2.27GHz带宽内,DPA功放在输出从饱和点回退2dB的动态范围内漏极效率均保持在50%以上,最大效率为59%,饱和输出功率在20W以上。回退效率值与仿真值基本相符,峰值效率有所下降,这主要由大信号模型与实际晶体管的差异所引起。

图6 20WDPA的(a)实际电路和(b)测试结果

4. 结论

在设计时考虑了Doherty功放的AM/AM、AM/PM特性,并且讨论了影响峰值功放开启时间的因素,进一步对功率配比和栅压进行了分析,并据此给出了回退效率空间的概念。基于GaN HEMT加工了一个功率配比为1:1的DPA,并进行了测试。测试结果表明,设计的DPA具有良好的效率,能够满足现代无线通信系统的应用。实测结果与仿真结果基本相符,证明了设计方法的正确性。