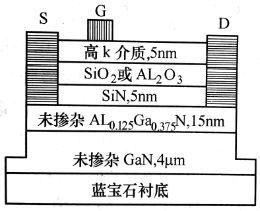

图1 MIS栅 Gan HEMT结构示意图

这里,高k介质是指HfO2,ZrO2和TiO2等介电常数较高的材料。

该器件的基本制造工艺及相关参数如下:

1) 使用2in蓝宝石衬底,用 MOCVD法沿衬底c轴方向顺序外延4μm不掺杂的GaN和15nm不掺杂的Al0.125Ga0.375N,二者的薄层电阻分别为10MΩ和420-510Ω。

2) 用RIE刻出元胞两侧的隔离台面。

3) 用电子束蒸发顺序淀积Ti/Al/Ni/Au,然后用快速退火法在780℃的氮气氛中退火30s,形成源和漏的欧姆接触。接触比电阻约为(3~5)x10-5Ω·cm2。

4) 用电子束蒸发在200℃下顺序淀积SiN钝化层(5nm)/氧化物层(8nm)/高k介质层(50nm)。

5) 用电子束蒸发顺序淀积Ni/Au形成栅电极。

测试结果表明,采用不同氧化物和不同高k介质的样管都有很好的直流通态特性。对栅长0.5μm、栅宽50μm、栅-源距2μm、栅-漏距4μm的所有样管,在栅压4V的测试条件下,漏极电流密度都在500~600mA/mm范围,跨导也都可以达到80~120mS/mm。但是,高k介质与SiN之间有没有氧化物对器件的断态(栅极加较高负偏压的状态)特性影响很大,采用有氧化物的MIS结构可使栅极漏泄电流减小一个数量级以上,漏极电流减小两个数量级左右。在栅长4μm、栅宽50μm、栅-源距2μm、栅-漏距28μm的有氧化物样管中,高k介质为HfO2者(无论氧化物为Al2O3还是SiO2)阻断电压高达1800V;高k介质为做ZrO2的样管中,氧化物为Al2O3者阻断电压也为1800V,氧化物为SiO2者阻断电压也可达1700V。