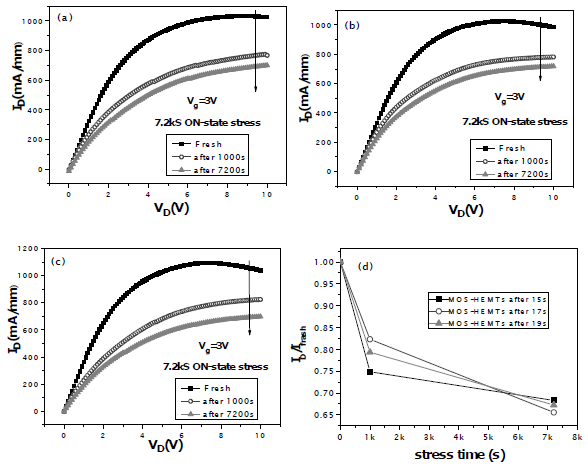

图1 (a)凹槽栅深度为0.62nm的MOS-HEMTs器件;(b)凹槽栅深度为2.71nm的MOS-HEMTs器件;(c)凹槽栅深度为3.25nm的MOS-HEMTs在7200s电学开态应力下的输出特性分析(栅压为3V);(d)器件输出特性退化量对比。

使用keithley4200scs半导体参数分析仪进行量测。其中开态应力是栅压为0V,漏压为20V,使器件长期处于导通状态。每个应力总时间为7200s,在这段时间中也测试器件特性(总测试十次,作图时取0s,1000s和7200s的数据),跟踪器件退化的详细过程。

图1所示的是不同凹槽栅深度的MOS-HEMTs器件在7200s的开态应力下输出特性退化的曲线图,随着应力时间的增加,器件输出特性也跟着退化,相比于线性区的退化,器件在饱和区的退化较小。器件在7200s开态应力后,线性区(膝点电压附近)输出电流退化量为42.2%,而在饱和区(漏压为10V)时退化量为30%。这是由于电学应力中,势垒层表面、体内和缓冲层内的陷阱会俘获一定量的电子,导致沟道导通电阻的增加,使得输出特性退化,而当器件的漏压较低时,导通电阻的增加效果很明显,使得输出电流退化量较大,当漏压较大时,导通电阻增加的影响被栅漏间的高电场所掩盖,使得器件在较高漏压时输出特性退化较小。对比三个凹槽栅深度的MOS-HEMTs器件在应力前后输出特性退化,从(d)图可知在1000s后,凹槽栅深度为0.62nm的MOS-HEMTs器件的退化量为最大25%,而在7200s应力后,三个凹槽栅深度的MOS-HEMTs器件退化量分别为,30%,32%和34%,退化量基本一样。

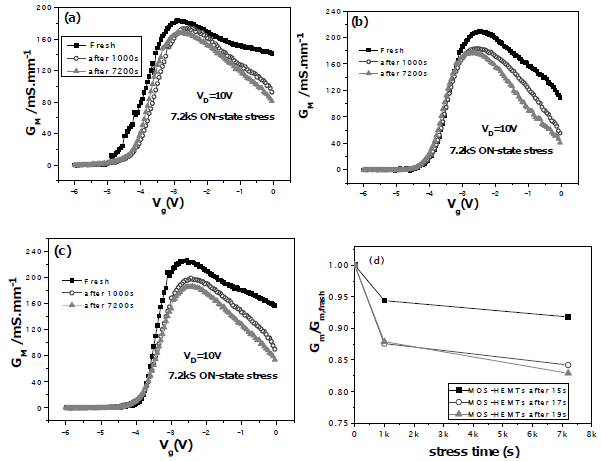

图2(a)凹槽栅深度为0.62nm的MOS-HEMTs器件;(b)凹槽栅深度为2.71nm的MOS-HEMTs器件;(c)凹槽栅深度为3.25nm的MOS-HEMTs在7200s电学开态应力下的转移特性分析(漏压为10V);(d)器件转移特性退化量对比。

图2所示不同凹槽栅深度的MOS-HEMTs器件在开态应力前后的转移退化情况,凹槽栅深度0.62nm的MOS-HEMTs器件应力前跨导峰值为183mS/mm,应力后1000s和7200s后其值172和168mS/mm,退化量分别为6.1%和9%;凹槽栅深度2.71nm的MOS-HEMTs器件应力前跨导峰值为209mS/mm,应力后1000s和7200s后其值183和176mS/mm,退化量分别为12.5%和15.8%;凹槽栅深度为3.25nm的MOS-HEMTs器件应力前跨导峰值为223mS/mm,应力后1000s和7200s后其值196和185mS/mm,退化量分别为12.1%和17.1%。我们发现,随着凹槽栅深度的增加,器件跨导峰值有所增加,从183mS/mm增加到223mS/mm,然而退化量也随之增加,从9%增加到17.1%,这说明了随着槽栅刻蚀产生的缺陷数量增加,器件跨导的退化量越大,这主要是由于缺陷俘获了栅上和沟道中的电子,在MOS结构间形成负电荷层,会屏蔽了栅到沟道的部分电场,使栅控能力的退化加剧。另外由于沟道热电子的产生,被势垒层表面和体内所俘获,二维电子气的限域性变差导致迁移率的下降,从而器件跨导特性退化。

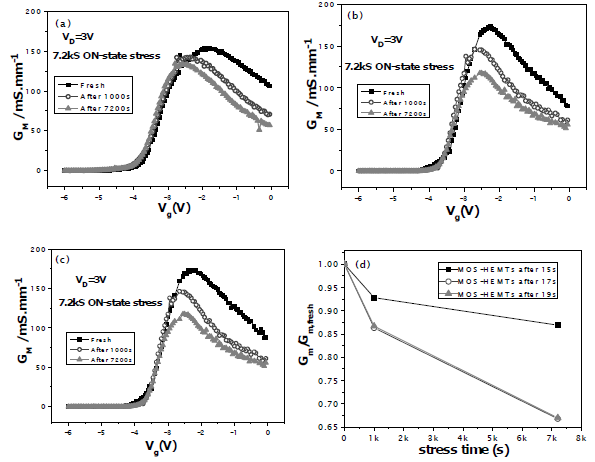

图3 (a)凹槽栅深度为0.62nm的MOS-HEMTs器件;(b)凹槽栅深度为2.71nm的MOS-HEMTs器件;(c)凹槽栅深度为3.25nm的MOS-HEMTs在7200s电学开态应力下的转移特性分析(漏压为3V);(d)器件转移特性退化量对比。

我们研究了不同凹槽栅深度的MOS-HEMTs器件在7200s开态应力前后的转移特性退化(漏压固定3V),如图3所示。凹槽栅深度为0.62nm的MOS-HEMTs器件的跨导应力前为153mS/mm,1000s应力和7200s后退化分别为142mS/mm和133mS/mm,退化量分别为7.2%和13.1%;凹槽栅深度为2.71nm的MOS-HEMTs器件的跨导应力前为169mS/mm,1000s应力和7200s后退化分别为146mS/mm和113mS/mm,退化量分别为13.7%和33.2%;而凹槽栅深度3.25nm的MOS-HEMTs器件的跨导应力前为173mS/mm,1000s应力和7200s后退化分别为150mS/mm和116mS/mm,退化量分别为13.3%和33.1%。随着应力时间的增加,跨导的退化量也随之增加,凹槽栅深度为2.71nm和3.25nm的MOS-HEMTs器件退化较大,因为三种器件都是同一圆片上的,所以由于热电子效应所导致的跨导退化量应基本一致,这退化量的增加可能是由于随着凹槽栅深度增加,刻蚀损伤导致MOS电容结构产生更多的界面态,加剧器件转移特性的退化。

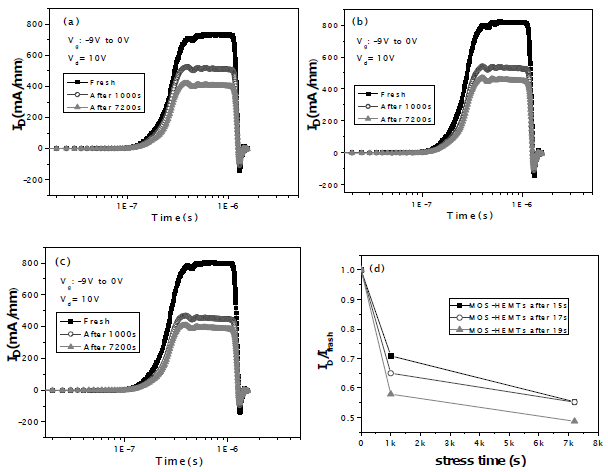

图4 (a)凹槽栅深度为0.62nm的MOS-HEMTs器件;(b)凹槽栅深度为2.71nm的MOS-HEMTs器件;(c)凹槽栅深度为3.25nm的MOS-HEMTs在7200s电学开态应力下的栅延迟特性(栅上脉冲从-6到0V,漏压固定在10V);(d)器件栅延迟特性退化量对比。

我们采用栅延迟测试来表征肖特基栅下区域陷阱的,栅上给脉冲电压信号,从-9V到0V,上升沿和下降沿的时间为150ns,脉冲周期10ms,脉冲宽度为500ns,占空比为5%。当栅上输入脉冲信号,由于栅下区域、势垒层和缓冲层的陷阱俘获的电子跟不上这脉冲信号,俘获的电子来不及释放导致沟道二维电子气浓度的减小,产生了栅延迟现象(电流崩塌)。如图4所示,我们发现三种凹槽栅深度的MOS-HEMTs在开态应力后都发生较为明显的栅延迟,凹槽栅深度为0.62nm的MOS-HEMTs器件开态1000s和7200s应力后退化量分别为70%和55.3%,凹槽栅深度为2.71nm的MOS-HEMTs器件的退化量分别为65%和55.2%,而凹槽栅深度为3.25nm的MOS-HEMTs器件的退化量为57.9%和48.7%。随着凹槽栅深度的增加,栅延迟现象益发明显,这与刻蚀损伤是相关的。