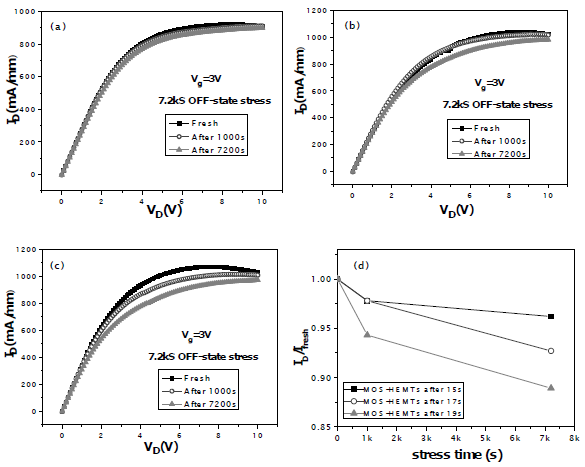

图1 (a)凹槽栅深度为0.62nm的MOS-HEMTs器件;(b)凹槽栅深度为2.71nm的MOS-HEMTs器件;(c)凹槽栅深度为3.25nm的MOS-HEMTs在7200s电学关态应力下的输出特性分析(栅压为3V);(d)器件输出特性退化量对比。

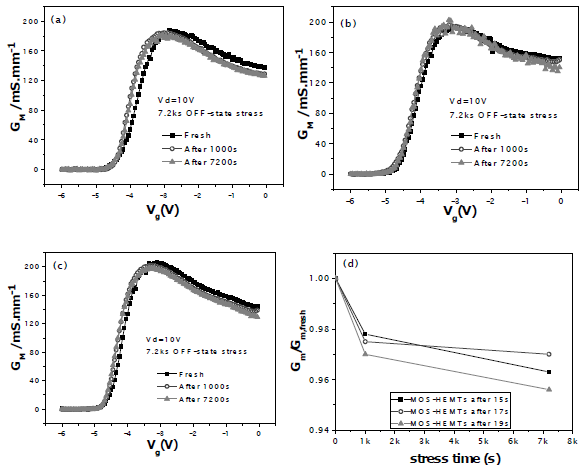

图1所示电学关态(-6V,20V)的应力前后,不同凹槽栅深度的MOS-HEMTs器件的输出特性退化情况。凹槽栅深度为0.62nm的MOS-HEMTs器件在1000s和7200s应力后退化量分别为2.2%和3.8%;凹槽栅深度为2.71nm的MOS-HEMTs器件的退化量分别为2.2%和7.3%;而凹槽栅深度为3.25nm的MOS-HEMTs器件的退化量分别为5.7%,11.1%。随着应力时间的增加,退化量有所增加,同时随着凹槽栅深度的增加,退化也有所增加,这有两部分的原因:a、关态时,沟道基本没有电子,不会发生热电子效应,但在栅漏间存在高的电场,这会使得势垒层发生逆压电效应,发生应力弛豫,产生新的陷阱,正是这些陷阱俘获了沟道的电子,降低了二维电子气的浓度,产生退化;b、栅漏间存在高电场,特别是在栅靠漏端的边缘处,电场峰值较高,而随着凹槽栅深度增加,栅下区域的界面态随之增加,这会使得栅极电子通过陷阱辅助隧穿被界面态所俘获,器件特性发生退化。图2所示,凹槽栅深度为0.62、2.71和3.25nm的MOS-HEMTs器件跨导退化量为2.2%、2.5%和3%(1000s关态应力后的退化量),3.7%、3%和4.4%(7200s关态应力后的退化量)。随着应力时间的增加,虽然在关态应力下沟道夹断没有产生热电子,但栅漏间存在高电场,可能导致逆压电效应产生新的陷阱,退化了二维电子气的迁移率,使得跨导特性退化。

图2 (a)凹槽栅深度为0.62nm的MOS-HEMTs器件;(b)凹槽栅深度为2.71nm的MOS-HEMTs器件;(c)凹槽栅深度为3.25nm的MOS-HEMTs在7200s电学关态应力下的转移特性分析(漏压为10V);(d)器件转移特性退化量对比。

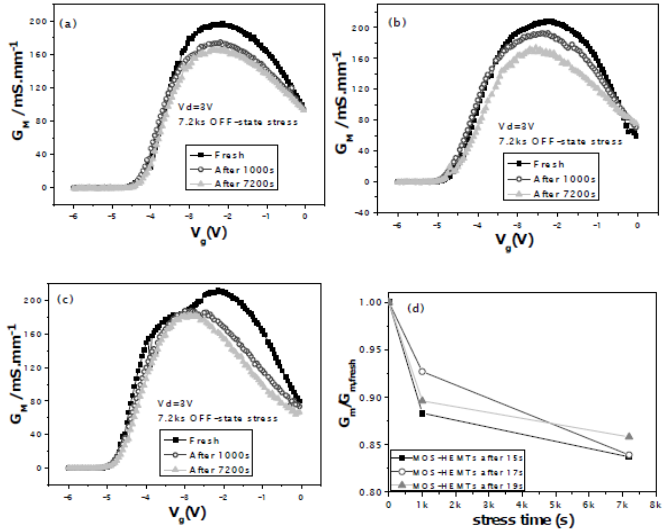

图3 (a)凹槽栅深度为0.62nm的MOS-HEMTs器件;(b)凹槽栅深度为2.71nm的MOS-HEMTs器件;(c)凹槽栅深度为3.25nm的MOS-HEMTs在7200s电学关态应力下的转移特性分析(漏压为3V);(d)器件转移特性退化量对比。

凹槽栅深度0.62nm的MOS-HEMTs器件转移特性(漏压为3V)跨导在关态1000s和7200s后退化量分别为11.7%和16.3%;凹槽栅深度2.71nm的MOS-HEMT器件在1000s和7200s应力后退化量分别为7.3%和16.1%;而凹槽栅深度为3.25nm的MOS-HEMTs器件的退化量分别为10.4%和14.2%。器件的阈值电压基本不发生漂移,关态应力下,沟道关断,虽然栅漏间存在高电场,但沟道可动电子很少,主要是栅极电子在栅漏间高电场作用下注入到AlGaN势垒层表面的陷阱形成的虚栅,而沟道基本不产生热电子,所以阈值电压基本没有发生退化。

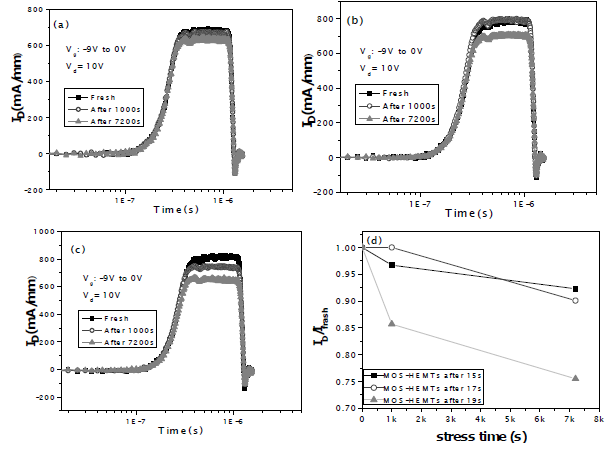

图4 (a)凹槽栅深度为0.62nm的MOS-HEMTs器件;(b)凹槽栅深度为2.71nm的MOS-HEMTs器件;(c)凹槽栅深度为3.25nm的MOS-HEMTs在7200s电学开态应力下的栅延迟特性(栅上脉冲从-6到0V,漏压固定在10V);(d)器件栅延迟特性退化量对比。

测试栅延迟时,栅上给脉冲电压信号,从-9V到0V,上升沿和下降沿的时间均为150ns,脉冲周期10ms,脉冲宽度为500ns,占空比为5%。如图4所示,我们发现三种凹槽栅深度的MOS-HEMTs在关态应力后栅延迟现象不严重,凹槽栅深度为0.62nm的MOS-HEMTs器件开态1000s和7200s应力后退化量分别为3.7%和7.7%,凹槽栅深度为2.71nm的MOS-HEMTs器件的退化量分别为0%和9.9%,而凹槽栅深度为3.25nm的MOS-HEMTs器件的退化量为14.3%和24.5%。我们发现随着凹槽栅深度的增加,栅延迟现象加剧,这与栅下区域的表面缺陷和界面态是相关的。