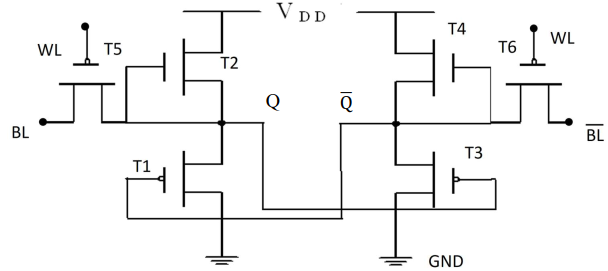

图1 GaN基E/D模SRAM单元电路图

GaN基E/D模6管SRAM单元电路由两个反相器和两个控制读取的晶体管组成,两个反相器相互将自己的输出端接到对方的输入端,通过正反馈将一个信号以互补的形式锁定在在电路中,通过字线(WL)控制管的通断来实现访问这个单元的信号。假设1存储在Q中,当处理器需要访问存储在这个SRAM单元的信号时,BL和`BL的电位被预先充电到1。字线WL读周期开始,WL上被加载一个高电平,T5和T6导通,BL维持自己的高电平电位不变;而`BL则需要尽快的通过向T3和T6放放电以将电位拉低到低电位。当BL和`BL的电压到达一定的差值时,被后级的灵敏放大器铺捉到,灵敏放大器将这个信号放大并传输到CPU等使用。

在读操作过程中容易发生的误操作之一是预充电的BL和`BL高电位在字线WL信号到来后,将错误的“1”写入`Q中去,T4为反相器的负载管,通常设计的电阻较大,所以`Q的电位在WL信号到来后由T6和T3的导通电阻比决定。如果`BL线上的电容过大,而T3和T6的电阻过于小,这使`BL放电更加缓慢。`Q电位依据T6和T3的电阻比可能到达离`BL电位较近的值,这将使得T1和T2组成的反相器的电流明显增大,造成SRAM存储单元状态的翻转。为了避免读过程的误操作,需要T3和T1的电阻值小于T5和T6的电阻值。定义单元比CR

SRAM写操作的过程描述如下。假设“1”存放在Q中,在WL有效状态下,通过在`BL上加高电平同时在BL上加低电平,可以将“0”写入SRAM单元中;在`BL上加低电平同时在BL上加高电平,相当于仍然将“1”写入SRAM单元中。仅考虑状态改变的情况。写操作开始时,两个反相器处于正反馈的稳定状态下,T1和T4漏极的电位被牢牢固定在高电平和低电平值。以上讨论过为防止读操作时的误写入操作,调整CR比以使得T5的电阻值比T1大。这样当字线WL到来时`Q的电压亦不会变得很高,改变SRAM单元电路的电平在另一侧T5进行。Q点的电压必须下拉得足够低,小于T1的阈值电压,才能把SRAM单元的状态翻转。由电路图看,Q点的电位在字线WL到来之时,由电路图看,Q点的电位在字线WL到来之时,由T4和T6的电阻比决定。反映到电路及器件的设计,为耗尽型负载管和增强型传输管的尺寸比决定,定义单元上拉比(PR):