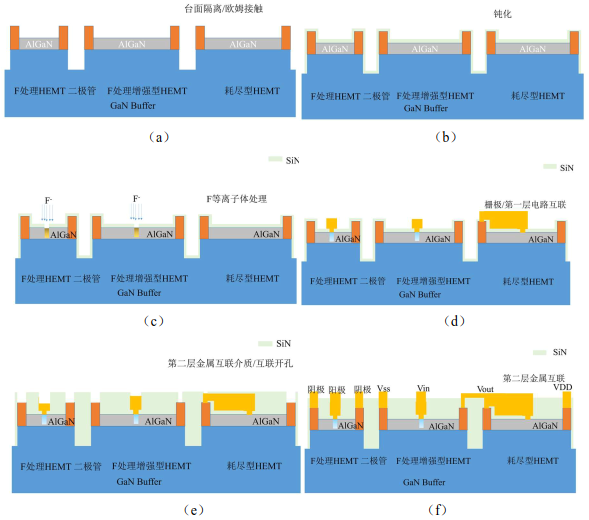

得益于F等离子体处理实现增强型器件的良好扩展性,GaN基E/D模电路可以在与原有器件工艺完全兼容的条件下完成。只需增加定义增强型栅形状的掩模版,以及增加为了稳定/老化F离子的栅后快速退火工艺。可以将栅极金属层部分定义为第一层金属互联。电路制备的工艺流程与器件的流程一致,依次为:晶片清洗,欧姆接触/源漏极定义,有源区隔离,钝化层淀积,增强型器件栅定义,耗尽型器件栅极定义,栅极金属淀积/第一层互联金属淀积,第二层互联金属介质淀积/互联开孔,第二层金属互联淀积。图1示意地画出了GaN基E/D模集成电路的工艺流程的关键几个步骤,图上完成的是F处理HEMT结构二极管及反相器电路。

图1 GaN基E/D模电路工艺示意图(a)台面隔离/欧姆接触(b)钝化层淀积(c)等离子体处理(d)栅极/第一层金属互联(e)第二层金属互联介质淀积/互联介质开孔(f)第二层金属互联。

电路制备的工艺流程从新片清洗开始,在开始工艺之前须对刚进行超净工艺间的外来晶片进行表面清洗和处理,主要目的是去除部分表面氧化物和有机物。首先将晶片放入丙酮中超声清洗2分钟,然后放入60℃的剥离液中加热10分钟。剥离液为光刻胶的清洗剂,有弱碱性,对有机物有一定的清洗作用。随后继续放入丙酮中超声清洗3分钟,乙醇中超声清洗3分分钟后,用与水的比例比例为5:1的氢氟酸(HF)处理晶片30秒。使用氢氟酸清洗的目的是为了去除晶片表面的部分氧化物。最后用超纯水冲洗2分钟并且用纯氮气彻底吹干晶片。

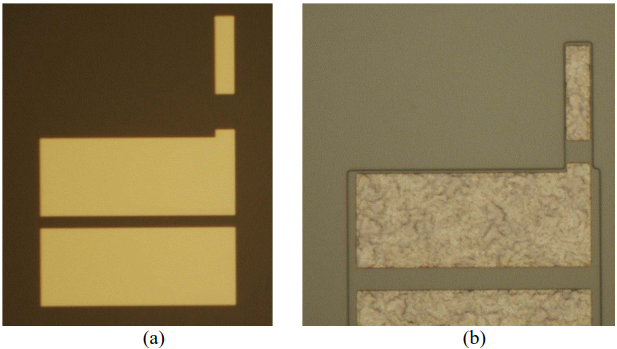

图2 (a)欧姆金属电子束蒸发沉积后显微镜下图像(b)退火后欧姆电极形貌

器件的源漏基由欧姆接触金属构成,采用电子束蒸发沉积的方式将四种金属(钛、铝、镍、金)按顺序和不同厚度依次淀积在晶片欧姆电极的位置。欧姆接触的第一层金属选择的是功函数较低的Ti,Ti的功函数为4.33eV,和AlGaN的接触形成较低肖特基势垒高度。第二层金属是为了防止Ti被氧化成Ti2O,同时阻止上层金属的向下扩散,第三层金属层为阻挡层,目的是为了阻挡最上一层金的扩散到势垒层表面退化欧姆接触质量。Ti/Al/Ni/Au金属堆叠层在温度高于800℃的氮气环境下退火约30秒后,能与AlGaN层形成良好的欧姆接触。在欧姆退火的过程中,Ti与AlGaN中的N原子反应形成TiN,因而在AlGaN层中形成了大量的N空位,这个过程在表面形成了高掺杂特征,有利于隧穿效应的发生。欧姆金属退火后的特性很大程度上和退火的温度和时间,金属层的厚度关系。退火温度过低,Ti的向下扩散效果差,不易形成低欧姆接触,退火温度过高,金属形貌恶化,影响其他层接触和器件性能。经过长期的实验,本实验室的Ti/Al/Ni/Au的厚度为22nm/140nm/55nm/45nm,退火温度为830℃ 30s。

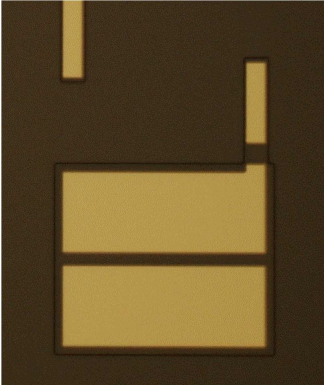

图3 台面刻蚀后显微镜下图像

随后进行的是有源区隔离工艺。通常电路的隔离工艺会选择平面隔离工艺的离子注入工艺。利用高能离子轰击非有源区,破环此区域的材料的晶体晶格结构,以达到耗尽自由电子的效果。离子注入有源区隔离工艺完成后整个材料表面仍然是平面,这将有效地降低电路中互联金属的垂直高度,明显的提高集成电路的成品率。通常选用He,H,N原子进行高能量轰击,也有报道使用F等离子体处理进行有源区隔离的文章,但是由于F离子对AlGaN和GaN有刻蚀作用,所以使用F等离子体处理的有源区隔离实际上也并非平面工艺。考虑工艺的兼容性,电路的有源区隔离工艺仍然采用工艺成熟的台面隔离工艺。使用RIE系统,以Cl2作为刻蚀气体,在100W的射频功率下刻蚀150s,刻蚀深度可达120nm,远远大于2DEG的深度,可以将各个有源区的2DEG完全隔离。台面刻蚀的需要注意的一点是,高能的离子轰击对器件表面造成损伤,表面的漏电会因此增加。尤其是在后续工艺SiN淀积完成之后,各有源区之间的漏电会比未进行钝化的有源区的漏电增加2~3个数量级,间隔5um的台面直接的漏电从原来的nA级增加到近uA级。这是因为SiN淀积的时候Si离子的向下扩散所造成的。晶体晶格破坏越大的表面越容易使Si扩散,造成一定程度上的Si掺杂。所以在RIE刻蚀的工艺不宜为了增加刻蚀速率而加大刻蚀处理的功率。折中工艺成本和器件性能的一个方法是进行两步刻蚀速率法,首先用相对较大功率对刻蚀区域进行刻蚀,到了一定刻蚀深度的位置改为相对较小的刻蚀速率进行。这样的处理能够明显改善SiN钝化后台面漏电严重增加的问题。

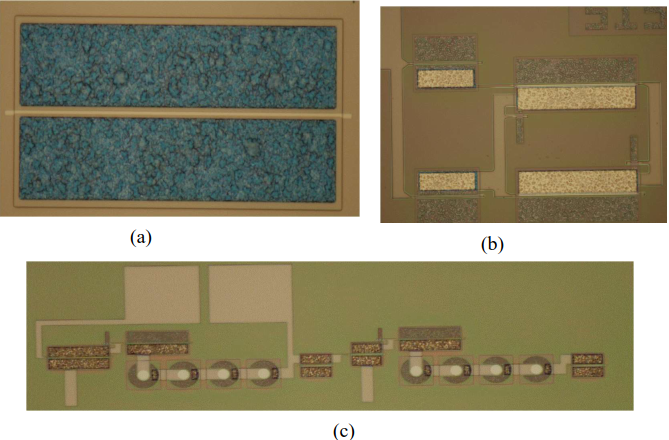

图4 栅极定义及第一层金属互联显微镜下图像(a)增强型栅槽刻蚀显微镜下图像(b)SRAM栅极及第一层互联光刻显微镜下图像(c)电平转换电路栅极极及第一层互联光刻显微镜下图像

在台面隔离完成之后进行的是SiN钝化层淀积工艺。钝化层的引入是为了消除或者减小HEMT器件中普遍存在的“电流崩塌”效应。HEMT器件表面存在着大量的表面态陷阱,这些陷阱在高频下的充放电跟不上栅极电信号的改变将引起栅下区域2DEG的部分耗尽,造成高频下的电流急剧下降的现象。SiN层的引入能显著的降低表面态的影响,大大地提高了HEMT器件在高频下的输出功率。本文使用的第一层的SiN的厚度为60nm,不仅作为抑制电流崩塌效应的钝化层,也作为T型栅的介质层。

SiN淀积后进行的是两种器件栅极的定义,首先用光刻机打开增强型器件的栅极区域,包括增强型器件的栅极和需要F处理的HEMT结构二极管的阳极。先对栅极上覆盖的SiN进行刻蚀,然后对栅极区域进行F等离子体处理。这两步工艺是在同一个RIE设备中连续进行的,第一步刻蚀SiN采用含O2的F等离子体处理,功率为50W;第二步F等离子体处理不含O2,处理的功率加到到120W,处理时间120秒。图4(a)显示的是增强型栅槽刻蚀后的照片,在进行了SiN刻蚀和F等离子体处理后,栅极区域线条完成,边缘清晰。随后打开耗尽型栅区域的SiN,进行的栅极金属淀积光刻。这一步同时也是电路的第一层金属互联层,SRAM单元电路的WL字线控制管输入,BL位线输出,电平转换电路的HEMT结构二极管串联也是使用栅极金属进行互联。图4(b)和图4(c)显示的是SRAM单元电路和电平转换电路的第一层金属光刻图。随后进行Ni/Au/Ni的栅极金属蒸发,和栅后300℃、8min的栅后快速退火以稳定F离子。

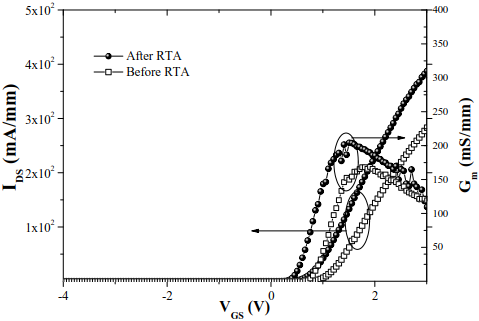

图5 300℃,8分钟栅后快速退火前后增强型器件输出特性曲线对比

图5所示的是300℃,8min栅后退火前后增强型器件的输出特性曲线对比图。可以看到退火前后的增强型器件的阈值电压往负向移动,从1.20V移动到0.80V,而饱和最大电流则从280mA/mm增加到了380mA/mm,最大跨导也相应的从155mS/mm增大到了230mS/mm。栅后快速退火是F等离子体处理实现增强型器件的关键工艺,虽然退火后阈值电压较退火前有-0.40V的漂移,但是退火却极大的改善了增强型器件的稳定性。栅后快速退火能将在势垒层中处于不稳定态的F离子进行重新排列,F离子在退火后处于一个相对稳定平衡的状态中。

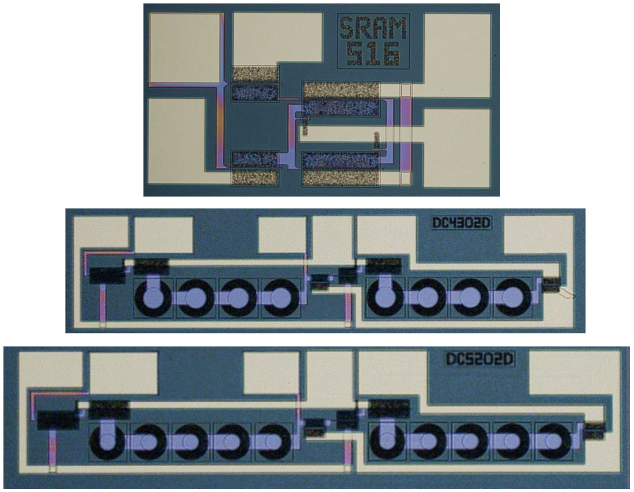

第二层金属互联的介质层采用器件兼容工艺的SiN层淀积,厚度为200nm。随后进行的是互联开孔刻蚀工艺,刻蚀条件同第一层SiN刻蚀的条件,最后是第二层互联金属的光刻和金属电子束蒸发淀积,整个电路的制备完成。图6显示的是完成后的SRAM单元电路和不同串联HEMT结构二极管数量的电平转换电路。

图6 最终完成的GaN基SRAM单元电路和电平转换电路