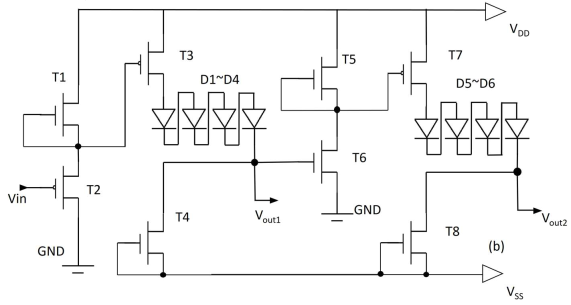

图1 GaN基E/D模电平转换电路图

电平转换电路的目标为将0V和5V的TTL输出电压转换约为-5V和0V,相对应于耗尽型HEMT的关断栅压和导通栅压。电路输出两路电压,一路为0V时另一路为-5V。电路拓扑结构见图1。由T1至T4组成电路的第一部分,和T5至T8组成电路的第二部分构成。第一部分的输入直接接TTL的逻辑输出,第二部分的输入部分同时也作为第一部分的负载。T2,T3和T7管为增强型器件,其余为耗尽型器件。

电路原理简述如下。T1和T2构成的E/D模反相器组成输入控制电路控制两路输出电压的翻转。当输入为低电平时,T3栅压为高电平,T3导通,VDD通过几个串联的HEMT结构二极管被拉低至0V左右,此电压作为Output1输出。Output1信号同时也连接在T6上,T6因此导通。设计T5和T6的电阻宽长比,将T5,T6组成耗尽型/耗尽型反相器。当T5导通输出低电平,当T5关断时输出高电平。当Output1为零时,T7关断,output2的由T8拉低到VSS。当输入高电平时,T1和T2组成反相器输出低电平,T3关断,Output1则由T4管拉低至Vss。此时负值的Output2将T6关断,T5和T6组成的耗尽型耗尽型反相器输出高电平,T7导通,VDD经过D5等几个串联的HEMT结构二极管被拉低到0V左右。

电路设计的关键点首先在于进行电压转移的HEMT结构二极管。始终有一半的HEMT结构二极管处于大偏置的工作状态下,其余的二极管偏置在反向。每个HEMT结构二极管的本征部分将降落1.34V的电压,如果加在HEMT结构二极管的电压超过1.34V,则其余部分将降落在寄生HEMT的源极和漏极上。如果要进行大于1.34V的电压转换,需要两个或多个HEMT结构二极管的串联。使用F处理HEMT管能够减小串联二极管的数量,但是由于F处理HEMT结构二极管在大电流密度的下出现的肖特基势垒降低的现象。因此在使用F处理HEMT结构二极管作为电压转移器件时,串联回路的总电阻值需要仔细设计,以确保流经F处理HEMT结构二极管的电流小于临界电流密度值。而设计串联回路总电阻的时候,增大总电阻也将增大在电阻上降落的电压,影响电压转换的精度。因此串联有源电阻/寄生HEMT有源电阻与HEMT结构二极管的个数设计需要进行折中考虑设计。其次,上拉管T3、T7与下拉管T4、T8的电阻比需要进行精确设计,T4和T8管的电阻需要设计得比T3、T7导通时高,以在T3、T7在导通时有足够的驱动能力拉高Output1和Output2的电压。