1. 表面态测试及计算原理

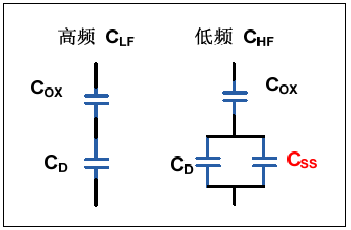

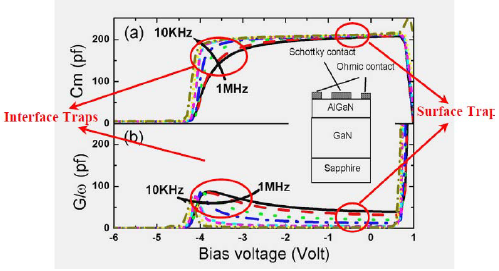

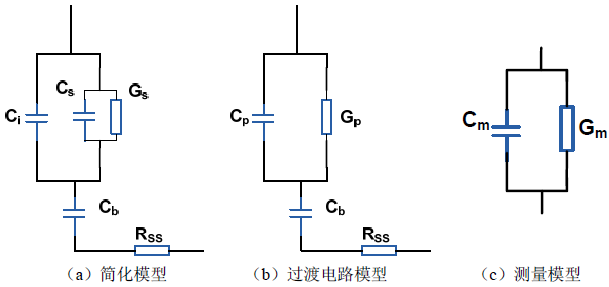

当器件外加电场V改变时,半导体表面势也发生改变,则表面处费米能级EF的位置也发生移动,导致表面态填充情况改变。表面态的充放电产生电容效应,因此对器件进行不同频率下的C-V测试,并将测试结果根据模型进行计算便可得到器件表面态密度D。对表面态计算研究的初期,一般采用MOS结构等效的纯电容模型进行表面态的测量和计算,如图1所示。

图1 AlGaN/GaN SBD表面态计算纯电容模型

表面态俘获和释放电子的时间小于测量信号周期时,才有电容效应。因此,采用准静态和高频相结合的方法进行测量,对测得的结果进行如式1的计算即可得到表面电容,进而得到表面态密度。

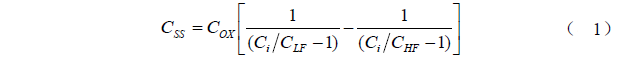

图2 AlGaN/GaN SBDC-G-V测量模型

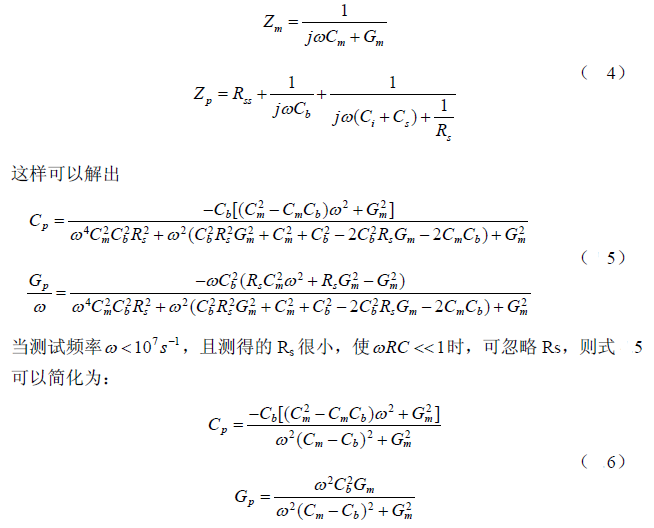

本文中C-G-V测试采用Agilent 4284A LCR,测试频率选取200、300、400、500、667、700、800、960及1000kHz,直流偏置电压范围为-3V~1V,步长为0.05V,交流小信号振幅为15mV,测量并记录每一C-V和G-V曲线。

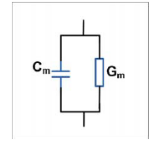

2. 表面态计算模型

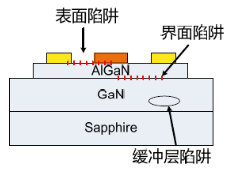

我们仿照MOS结构的分析方法来讨论AlGaN/GaN中缺陷的种类。如图3所示,在AlGaN/GaN SBD中主要存在GaN缓冲层陷阱、AlGaN-GaN的界面陷阱和AlGaN表面陷阱。因为缓冲层中的缺陷能级一般处于禁带中较深的能级处,充放电时间较长,因此在本文中忽略其影响,只考虑表面陷阱和界面陷阱的充放电影响。

图3 AlGaN/GaN SBD缺陷的种类及位置

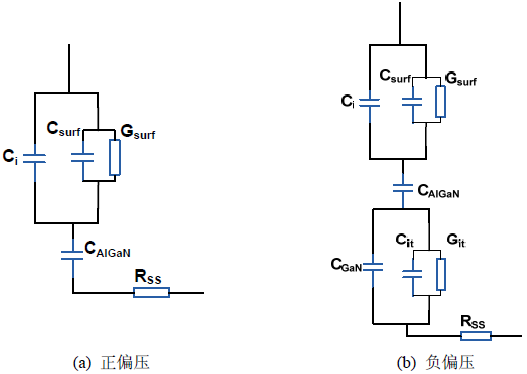

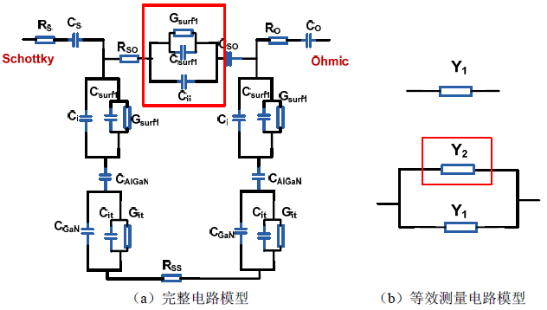

在同时考虑表面态和界面态时,由于Schottky电极的控制作用,在接近零偏压处及正偏压范围内,因为AlGaN-GaN界面处大量的2DEG聚集,因此在不同频率下测得的C-V、G-V曲线在零偏压附近的差异就反映了AlGaN表面处不同能级表面态的信息如图4所示,其正向偏压下的等效电路图如图5(a)所示。Csurf、Gsurf分别为表面态等效的电容和电导,Ci分为表面氧化层电容,因为表面氧化层非常薄,一般Ci可忽略不计。Cit分Git界面态等效的电容和电导,Rss为串联电阻。开始时沟道内的2DEG的浓度很高,器件的电容相当于AlGaN层的平板电容,因此保持不变。当反向偏压很大时,电容逐渐减小,这是因为沟道处2DEG浓度逐渐降低,所以要考虑GaN区的电容,不同频率C-V、G-V曲线在较大负偏压下的差异反映了AlGaN-GaN界面处界面态的信息,如图4所示,其等效电路见图5(b)。

图4 AlGaN/GaN SBD C-V、G-V测试曲线

对比图5(a)与5(b),可以看出,利用负偏压下的测得的阻抗值Z减去零偏压附近阻抗值Z(0),即可求得ZGaN。接下来需要解决的问题是测量值Cm、Gm与等效模型中的各参数之间的换算。

图5 AlGaN/GaN SBD表面态等效模型

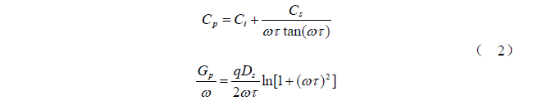

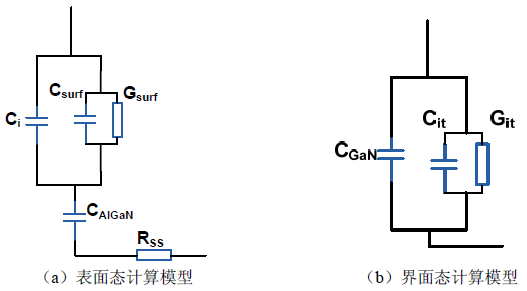

由图6可以看出,分别用以计算表面态和界面态的电路模型在结构上相似,因此我们利用图7(a)中的电路进行统一讨论。此外,为建立图6(b)中电路Cs、Gs与Cm、Gm,进而求得Ds和τ,我们引入一个过渡电路模型,如图7(b)所示。根据E.H.Nicollian等人的的研究,在某一连续能级上,有关系:

由式2可以直接根据Cp、Gp求得表面态浓度Dit和相应时间常数τ。时间常数τ越大,表示对应在禁带内的能级越深。

图6 表面态、界面态计算模型

图7 等效计算模型

Cp、Gp与Cm、Gm的换算关系可以根据电路原理进行直接的串并联转换。根据图7(a)中两图,对于计算界面态的电路,可知因Ci和Rs均为零,则:

Cp=Cm

Gp=Gm (3)

对于计算表面态的电路,两电路阻抗值相等Zm=Zp,且

3. 实验及计算结果

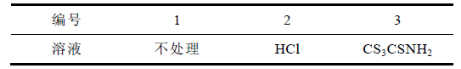

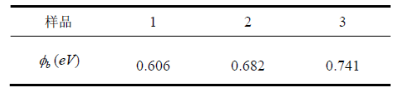

实验共三片样品,分别采用表1中所列的表面处理方法。

表1 表面处理后各样品的比接触电阻率

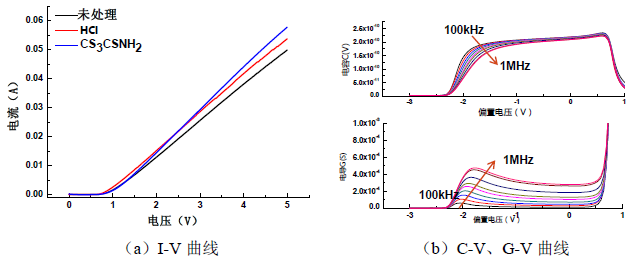

图8 测试曲线

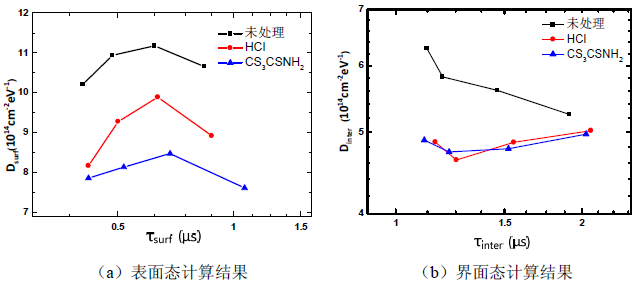

通过拟合和计算得到势垒高度φb列在表2中,表面态Dsurf~τsurf曲线以及界面态Dit~τit曲线如图9。

表2 表面态计算所得参数

图9 表面态、界面态计算结果

由表2中数据可得,经过表面处理势垒高度明显增高,优化了肖特基接触质量。由图9(a)所示结果,Dsurf和τsurf分别在1014~1015cm-2eV-1和0.4~1µs范围内,且经过表面处理后,表面态密度有了明显的降低。这是因为,利用溶液进行表面处理,不但能够去除表面氧化层,而且可以降低表面态密度,减弱半导体表面的费米能级钉扎对肖特基接触的影响。从图9(b)中可以得到,Dit和τit分别在1014cm-2eV-1和0.4~2µs范围界面态密度没有发生明显的变化,这是因为表面处理对AlGaN/GaN异质结界面没有直接的作用,但是表面能级发生变化导致表面势的变化,同样会对AlGaN/GaN界面处产生微弱影响。

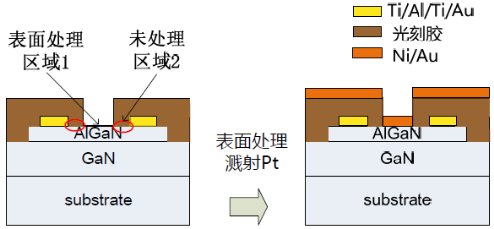

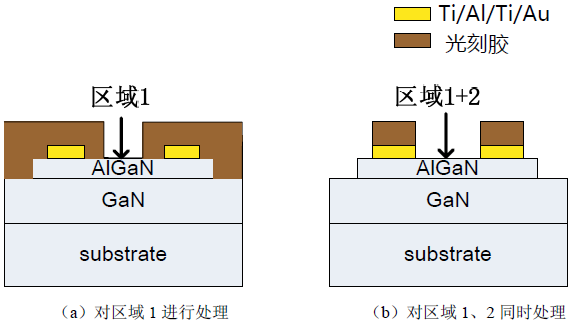

肖特基接触制作前表面处理的区域如图10中所示。此过程只考虑了直接与肖特基电极接触的AlGaN表面的性质,而未考虑肖特基电极与欧姆电极之间半导体的表面性质对器件性能影响,如图10中红色线所标注的区域。

图10 肖特基接触表面处理的区域

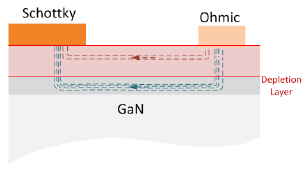

上图中区域1的表面态主要是影响金属与半导体肖特基接触的质量,如反向击穿电压及反向漏电流。而区域2处的表面态,除了在反向偏置时提供了一条新的漏电通道,如图11,还在器件表面形成了浮栅效应,使器件工作时的电流低于理论值。

图11 反向偏置时的漏电通道

为了研究这两个区域表面态的不同作用,本文设计了一套新的对比实验工艺过程。如图12所示,图中列出表面处理这一步骤的对比图,(a)中的处理区域同前面提到的区域1,而(b)中采用制作欧姆接触时的模板图形,利用负胶经过光刻覆盖住已经制作好的欧姆接触金属,对其余区域进行表面处理。

图12 对比实验中关键工艺过程—表面处理

在器件制作完成后,进行如下测试和仿真计算:

(1)I-V测试。对比反向漏电流的大小,研究不同漏电通道的影响。

(2)C-V测试。根据对比实验,提出了相应的计算模型。如图13(a)所示,模型中大部分电路图与2. 节中的模型相同,为计算区域2处的表面态密度,在电路中引入了图中红线标注的电路结构。因为AlGaN/GaN SBD是横向器件,当考虑肖特基电极和欧姆电极之间的半导体表面性质时,等效电路就不能如2. 节中一样只取对称电路的一半进行计算。当忽略接触电阻的影响,只需将分别测得的导纳值相减就可以得到区域2的表面态等效导纳,测试原理图如图13(b)所示。

(3)AlGaN/GaN异质结界面2DEG浓度的计算。通过对比计算所得的2DEG浓度,讨论区域2中表面态产生的虚栅对2DEG浓度的影响。

图13 对比实验的表面态计算模型

结合以上分析方法,可以研究肖特基电极和欧姆电极之间半导体表面性质对器件的影响。此部分内容为AlGaN/GaN SBD表面态的进一步研究提供一种新思路,尚待实验进行验证。